CPLD обясни: Ръководство за програмируеми логически устройства

В динамичния свят на електронния дизайн сложните програмируеми логически устройства (CPLDS) се открояват като многостранни инструменти, безпроблемно смесват адаптивността, прецизността и ефективността.Тези устройства революционизираха дизайна на веригата чрез въвеждане на програмируеми макро клетки и доминираща матрица за свързване, което позволява създаването на сложни логически функции със забележителна надеждност.От създаването им през 80 -те до ключовата им роля в съвременните индустрии като мрежи, автомобилни и аерокосмически, CPLD са доказали необходимите за вас, които търсят както гъвкавост, така и ефективност.Тази статия се разкопава в пътуването на CPLD, техните отличителни характеристики, практически приложения и методологиите за програмиране, които ги правят крайъгълен камък в дигиталния логически дизайн.Каталог

Преглед на CPLD

В рамките на доминирането на сложни програмируеми логически устройства (CPLDS) човек открива сложен гоблен от програмируеми логически макро клетки, преплетени чрез доминираща матрица на взаимосвързаност.Тези единични линии на макро клетки (MC) и вход/изход (I/O) ви позволяват умело да проектирате вериги, като конфигурирате структурите за уникални функции.За разлика от устройствата, които са озадачени от сложното им взаимосвързаност, CPLD използват недвижими метални проводници.Тази характеристика им дава последователно и предвидимо поведение на часовника, което прави прогнозите за времето по -надеждни и прецизни.

Пътуването и използването

70 -те години на миналия век обявиха появата на програмируеми логически устройства (PLDS), насърчавайки преминаването към програмируеми макро единици.Тази промяна въведе широка гъвкавост на дизайна, като ги отделя от статичните цифрови схеми, въпреки че тяхната програма първоначално беше ограничена до по -прости вериги.Появата на CPLD в средата на 80-те години революционизира този пейзаж, проправяйки пътя към сложните дизайни на вериги.Оттогава те са се вписали в тъканта на индустрии като мрежи, автомобилна електроника, обработка на ЦПУ и аерокосмически системи.Можете да си припомните начина, по който CPLD опростяват процесите, които веднъж поискаха щателен ръчен труд, отбелязвайки забележителен скок в ефективността.

Отличителни качества на CPLD

CPLDS се отличават чрез своето адаптивно програмиране, обширна интеграция, възможности за развитие на бързи разработки и широко приложимост, заедно с икономичните производствени разходи.Те се харесват на тези с минимално хардуерно изживяване, служещи като надеждни и сигурни продукти, които не изискват изчерпателни тестове.Като свидетелство за тяхната доблест в мащабните дизайни на вериги, CPLD играят ключова роля в разработването на прототип и обслужват под 10 000 единици, въплъщавайки полезна компетентност за вас.Адектът, с който CPLDS се приспособява към развиващите се изисквания на проекта, често им печели признателност, като подчертава действителната им гъвкавост в динамичната среда.

Методи на приложение

Тези интегрални схеми ви позволяват да разяснявате логически функции, съобразени с техните нужди, използвайки както схеми, така и езици за описание на хардуер на платформи за разработка.Например, при проектирането на телефонен секретар, схеми и хардуерни описания се подготвят и съставят на компютър.Използвайки кабел за изтегляне, кодът се прехвърля в CPLD за програмиране в системата, което включва тестване, отстраняване на неизправности и подобряване на дизайна.След това успешно изработените дизайни се произвеждат масово чрез репликиране на CPLD чипове.В проекти като системи за светофар, повтарянето на процеса на проектиране става необходимо, подобно на възстановяването на къща за възстановяване на своята новост.Тази повтаряща се методология често поставя основите за овладяване, засилване както на уменията, така и увереността.

Водещи варианти

През годините компании като Altera, Martice и Xilinx разкриха видни линии на CPLD.Забележителните примери включват Altera's EPM7128S, Решетка LC4128V, и на Xilinx XC95108 .Тези модели са открили видни роли в различни глобални приложения.Тези, които са имали привилегията да работят с тези различни продукти, често отбелязват фините, но мощни разлики, които оптимизират определени функционалности.Това отразява финия процес на подбор, повлиян от конкретни изисквания на проекта, където всеки вариант има своята уникална привлекателност.

Идентификация и класификация на FPGA и CPLD

|

Аспект |

Cpld |

FPGA |

|

Формиране на логическо поведение |

Формирайте логическо поведение, използвайки структура на продукта.

Примери: Серия ISPLSI на решетката, серия Xilinx XC9500, Altera Max7000s

серия, решетъчна серия от маха |

Формирайте логическо поведение, използвайки метод за търсене на таблица.

Примери: Spartan Series Xilinx, Altera Flex10k, серия ACEX1K |

|

Годност |

Подходящ за алгоритми и комбинирана логика, работи

по -добре с ограничени задействания и богати думи на продукта |

Подходящ за последователна логика, работи по -добре с

Структури, богати на задействания |

|

Забавяне на времето |

Непрекъснато структурата на окабеляването осигурява равномерно и

предсказуеми забавяния на времето |

Сегментираната структура на окабеляването води до непредсказуемо време

закъснения |

|

Гъвкавост на програмирането |

Фиксираните вътрешни вериги са модифицирани за програмиране.

Използва се програмиране на логически блок |

Вътрешното окабеляване е модифицирано за програмиране.Логика

Програмирането на ниво порта позволява по-голяма гъвкавост |

|

Интеграция |

По -ниска интеграция в сравнение с FPGA |

По -висока интеграция с по -сложна структура на окабеляване и

Изпълнение на логиката |

|

Лесна употреба |

По -лесно за използване с програмиране чрез E2Prom или FastFlash.

Не се изисква чип за външна памет |

Изисква външна памет за съхраняване на програмиране

информация, което води до по -сложна употреба |

|

Скорост и предсказуемост |

По -бърза скорост и по -добра предсказуемост на времето поради

Включена връзка между логическите блокове |

По -бавна скорост и по -малко предвидимо време поради

Програмиране на ниво на портата и разпределена връзка |

|

Технология за програмиране |

Използва програмиране на E2Prom или флаш памет.Данни за програмиране

се запазва, когато системата се изключи.Поддържа програмиране на a

програмист или в системата |

Въз основа на програмирането на SRAM.Данните за програмиране се губят, когато

Системата се изключва и трябва да бъде презаредена.Поддържа динамична

конфигурация |

|

Поверителност |

Предлага по -добра поверителност |

Осигурява по -ниска поверителност |

|

Консумация на енергия |

Като цяло по -висока консумация на енергия, особено с

по -висока интеграция |

По -ниска консумация на енергия в сравнение с CPLD |

Езици на програмиране на CPLD

Анализирането на програмирането на сложните програмируеми логически устройства (CPLD) е крайъгълен камък в изработването на универсални хардуерни решения.Историческите методи за програмиране CPLD са разчитали на диаграми на стълбата или езици за описание на хардуер (HDL), като Verilog HDL и VHDL са преобладаващи избори.Избраният език може да оформи както стратегията за проектиране, така и оперативната ефективност на реализациите.

• Verilog HDL: Verilog HDL е ценен заради простия си синтаксис и стабилни симулационни възможности, отразявайки методологиите, използвани в дигиталния логически дизайн.Неговата интеграция с инструменти за автоматизация на електронния дизайн (EDA) ви позволява безпроблемно да провеждате синтез и симулация.Наблюдава се, че синтаксисът на C Verilog е наблюдавано, че намалява бариерата за влизане за тези с програмиращ фос, ускорявайки пътуването от дизайн до внедряване в широк спектър от индустриални сектори.

• Vhdl: VHDL предоставя по -сложна и изразителна опция за HDL програмиране.Често изборът за проекти изисква щателна документация и строга проверка на типа, черти, оценени в аерокосмическата и отбранителната индустрия.Можете да отбележите, че въпреки потенциалната сложност на VHDL в по -малките проекти, неговата дисциплинирана структура подкрепя създаването на изключително надеждни дизайни, необходимост в среди, където безопасността е доминираща.

За нас

ALLELCO LIMITED

Прочетете още

Бързо запитване

Моля, изпратете запитване, ние ще отговорим незабавно.

NMOS транзистори: Дизайн, работа и приложения

на 2024/12/29

Бързата трансформация на Фурие (FFT): Революционизиране на обработката на цифровия сигнал

на 2024/12/29

Популярни публикации

-

Компютри на сложни инструкции: Как промениха изчисленията?

на 8000/04/18 147774

-

USB-C Pinout и функции

на 2000/04/18 112017

-

Използване на Xilinx Unified Simulation Primitives: Изчерпателно ръководство за FPGA дизайн и симулация

на 1600/04/18 111351

-

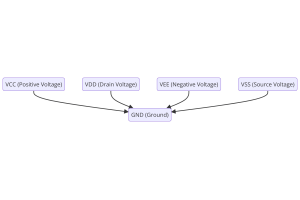

Захранващи напрежения в електрониката: Значение на VCC, VDD, VEE, VSS и GND

на 0400/04/18 83771

-

Ръководство за конектор RJ45: Pinout, окабеляване, видове кабели и употреби

на 1970/01/1 79568

-

Крайното ръководство за цветни кодове в съвременните електрически системи

Начинът, по който нашите електрически системи използват цветове, не е само за външен вид.Всеки цвят на проводника сега показва специфична функция, което улеснява идентифицирането и обработката на е...на 1970/01/1 66961

-

Ръководство за клапа на чист: функция, симптоми, тестване и подмяна на оптимална работа на двигателя

Клапанът на чистката е ключова част от системата на автомобила, която помага да се поддържа чистият въздух, като управлява изпаренията на горивото, преди да могат да избягат в атмосферата.Това не с...на 1970/01/1 63102

-

Качество (Q) Фактор: Уравнения и приложения

Коефициентът на качество, или „Q“, е важен при проверка на това колко добре работят индуктори и резонатори в електронни системи, които използват радиочестоти (RF).'Q' измерва колко добре веригата с...на 1970/01/1 63041

-

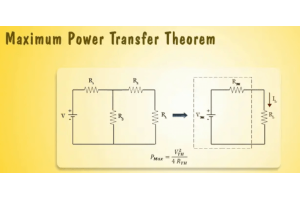

Постигане на пикова ефективност с теоремата за максимален трансфер на мощност

Теоремата за максимален пренос на мощност обяснява как енергия от източник, като батерия или генератор, преминава към свързан товар.Той показва точното състояние, при което товарът получава най -мн...на 1970/01/1 54097

-

Спецификации и съвместимост на батерията A23

Батерията A23 е малка батерия с форма на цилиндър с високо напрежение.Нарича се още 23A, 23AE или MN21, той работи на 12 волта и много по -високо от батериите на AA или AAA.Специалният му ...на 1970/01/1 52185