Изчерпателно ръководство за TestBenches: Инструменти и техники за проверка на цифровата система

Това ръководство изследва TestBenches, ключов инструмент за валидиране на софтуера, който симулира условията за тестване на входовете и проверка на резултатите.TestBenches играят роля за идентифициране на бъгове в началото на развитието, подобряване на надеждността на софтуера.С практически примери и прозрения, тази статия подчертава тяхната употреба, техники и значение за изграждането на силни, ефективни цифрови системи.Каталог

Ролята на тестовете в валидирането на цифровата система

TestBench е компонент в процеса на валидиране на цифровата система.Това не е просто инструмент за генериране на входове и проверка на резултатите, той служи като цялостна рамка, която симулира условията за оценка на надеждността, функционалността и поведението на цифровите системи, преди да бъдат внедрени в полето.Чрез създаване на контролирани среди към системи за тестове на стрес с широк спектър от входни сценарии, TestBenches ви помагат да идентифицирате потенциалните недостатъци на дизайна в началото на жизнения цикъл на развитието, много преди системата да бъде пусната в производството.Това ранно откриване на бъгове и уязвимости е необходимо за намаляване на скъпите грешки, гарантиране на спазването на спецификациите на производителността и подобряване на общата надеждност на системата.

В допълнение към проверката на правилността на отговорите на системата, TestBenches играят роля при оценката на крайните случаи, проблемите на времето и механизмите за обработка на грешки, като се гарантира, че системата може да работи правилно дори при екстремни или неочаквани условия.Чрез автоматизирано тестване и симулация, TestBenches допринасят за по -високо качество на софтуера, подобрена производителност и по -кратки цикли на развитие, като позволяват итеративно тестване без ръчна намеса.Те служат като предпазна мярка срещу неуспехи, които биха могли да възникнат след внедряване, като гарантират устойчивостта и надеждността на цифровите системи.

Основни компоненти на тестова лента и техните функции

За да разберете по -добре как функционират testbenches, е важно да се изследват компонентите, които ги правят ефективни.Добре изработената тестова маса работи, като управлява две основни задачи: генериране на входове (стимули) и проверка на резултатите.Нека разгледаме подробно всеки компонент.

Генериране на стимули

Генерирането на стимули включва създаване на набор от входни сигнали, които симулират условия за тестване на поведението на цифрова система.Тези входове трябва да бъдат както прецизни, така и реалистични, за да се гарантира, че системата е подложена на различни сценарии, които може да срещне на практика.Помислете за основен RAM модул като пример.TestBench трябва да доставя специфични входове на модула и да наблюдава своите резултати, за да се гарантира, че се държи както се очаква.Ключовите входове за RAM модул обикновено включват:

• CLK (часовник): задвижва времето на системата.

• ADDR (адрес): Посочва до кое местоположение на данните за достъп.

• WEN (активиране на запис): Контролира дали данните са написани в паметта.

• Данни: Действителната информация, написана на модула.

Изходът, известен като Dataout, представлява резултата от вътрешните операции на модула.Чрез внимателно скриптове как се доставят тези входове и наблюдават данни, можете да проверите дали системата се представя правилно при различни сценарии.Помислете за генерирането на стимули като създаване на тестов сценарий в лаборатория.Точно както учените внимателно контролират условията, за да наблюдават химичните реакции, цифровите дизайнери изработват прецизни входове, за да наблюдават как реагира системата.

Проверка на изхода

Проверката на изхода е процесът на проверка дали действителните изходи на системата съответстват на очакваните резултати.Тази стъпка е от решаващо значение за улавяне на грешки рано, преди да се превърнат в по -големи проблеми.Други използват проверка на изхода, за да потвърдят, че системата отговаря на предвидената му функционалност и се изпълнява последователно при различни условия.Проверката на изхода включва както автоматизирани, така и ръчни проверки.Например:

• Автоматизирани инструменти за проверка: Инструменти като Modelsim и Quartus позволяват автоматизирано тестване, където изходите на системата се сравняват с очакваните резултати.Това ускорява процеса на проверка и намалява грешката.

• Ръчна проверка (незадължителна): За по -сложни сценарии може да са необходими ръчни проверки, за да се гарантира, че специфичните случаи на ръба са обхванати.

Инструменти и техники за изпълнение на TestBench

Кварт: Визуална входна/изходна симулация

Quartus осигурява графичен интерфейс, който визуално подрежда входовете и наблюдават изходи.Този метод може да бъде полезен за начинаещи или за системи, които изискват по-практичен, визуален подход.Позволявайки да взаимодейства със симулация чрез графична среда, Quartus помага да се демистифицира връзката между входовете и изходите, като улеснява разбирането на това как се държи цифрова система във времето.Една от ключовите силни страни на квартуса е, че е идеален за начинаещи.Неговият интуитивен, визуален интерфейс осигурява лесен начин да видите как входовете влияят на изходите, без да е необходимо обширни знания за скриптове или програмиране.Обратната връзка, която предлага, помага да се разбере по -лесно поведението на веригите, което го прави полезен инструмент за тези, които са нови в дизайна на цифровата система.Квартусът обаче има своите ограничения.Настройването на симулации в кварта може да отнеме много време, особено за по-сложни дизайни.Инструментът е по-малко гъвкав в сравнение с инструментите за симулация, базирани на скриптове, които могат да предложат повече опции за персонализиране и автоматизация.За работа по мащабни или много подробни системи, тази липса на гъвкавост може да представлява предизвикателство.

Modelsim: Текстова симулация с помощта на скриптове

ModelsIM използва различен подход за симулация, като приоритизизира текстовото базирано въвеждане чрез скриптове.Създайте тестови сценарии с помощта на скриптове Verilog (.V) или VHDL (.VHD), а не визуално подреждане на входове и изходи.Този метод осигурява повече прецизност и контрол.Вместо да разчитате на графичен интерфейс, вие определяте как системата трябва да бъде тествана чрез подробни скриптове, което позволява по -голямо персонализиране и автоматизация в процеса на симулация.Една от основните силни страни на Modelsim е гъвкавостта, която предлага.Използвайки скриптове, имате повече контрол върху сценариите за тест, което им позволява да създават сложни и прецизни симулации.След като дизайнер е запознат със синтаксиса и работния процес, настройването на симулации може да бъде много по -бързо в сравнение с използването на графични инструменти като Quartus.Способността за повторна употреба и промяна на скриптове също добавя към неговата ефективност, особено в по -големи проекти.Текстовият подход на ModelSIM обаче идва с определени ограничения.Той изисква солидно разбиране на синтаксиса на Verilog или VHDL, което може да представлява предизвикателство за начинаещи, които не са запознати с езиците на хардуерното описание.В резултат на това ModelsIM има по -стръмна крива на обучение в сравнение с повече инструменти за визуална симулация.Новите потребители може да затруднят да започнат, но с практиката прецизността и гъвкавостта, предлагани от скриптовете, могат да се превърнат в ценен актив.

Мостови теория и практика при проверка

TestBenches служат като мост между теоретичните дизайни и приложения, като симулират как цифровата система ще се държи при различни условия, включително крайни случаи и неочаквани входове.В дигиталния дизайн често е трудно да се предвиди как една система ще се представи на практика въз основа само на теоретични модели.TestBenches затворете тази празнина, като ви позволяват да преминете отвъд абстрактните дизайнерски концепции и да оцените поведението на системата в контролирана, симулирана среда.Едно от основните предимства на използването на инструменти за симулация в TestBenches е моменталната обратна връзка, която предоставят по време на отстраняване на грешки.Инструменти като MultiSIM или ModelsIM предлагат визуални представи за поведението на системата, показващи как промените във входовете влияят на резултатите във времето.Тази обратна връзка ви позволява да определяте проблеми по -бързо, да проследите грешки обратно към основната им причина и съответно да коригирате дизайна им.Например, ако една система не изпълни ограниченията на времето или проявява неочаквано поведение при определени входни последователности, тестовата лента може да подчертае тези недостатъци веднага, преди да се изгради физически системата.Чрез идентифициране на проблеми в началото на цикъла на проектиране, TestBenches намалява необходимостта от скъпо преработка и физическо прототипиране, оптимизиране на процеса на проверка.Това валидиране на ранен етап помага да се гарантира, че цифровите системи са функционално коректни и устойчиви на условия, което ги прави по-надеждни и намалява риска от неуспех след внедряване.По този начин TestBenches действат като практичен инструмент за трансформиране на теоретични дизайни в стабилни.

Усъвършенствана архитектура на TestBench

Разширените TestBenches надхвърлят простото тестване на вход-изход, като включват допълнителни компоненти за управление на сложни системи.Стандартният тест включва три ключови части: a Генератор на стимули За да създадете входни сигнали, a Дизайн в тест (DUT), който е действителният хардуер, който се тества, и Изходен монитор Това проверява резултатите спрямо очакваните резултати.Тези компоненти работят заедно, за да осигурят по -задълбочена и точна проверка на цифровите дизайни.

Подобряването на точността на TestBench включва използването на техники, които гарантират, че дизайнът се представя надеждно в различни сценарии. Рандомизирано тестване Въвежда непредсказуеми модели на вход, за да провери стабилността на системата при различни условия. Тестване на дело на ръба Фокусира се върху граничните ситуации, при които системата е най -вероятно да срещне грешки.И накрая, Регресионно тестване Включва повторни тестове след промени, за да се потвърди, че не са въведени нови проблеми, като се гарантира, че системата остава последователна и без грешки във времето.

Скриптове за тестове

За да създадете ефективни и надеждни тестове във Verilog или VHDL, следвайте ключови най -добри практики.Започнете просто, след това разширете, като тествате основната функционалност първо и постепенно добавяте по -сложни сценарии.Използвайте коментари и документация, за да направите вашите скриптове по -лесни за разбиране и поддръжка, като ясно обясните всеки раздел.И накрая, автоматизирайте, когато е възможно, за да спестите време и да намалите грешките, като използвате контури и функции за справяне с повтарящи се задачи и модели на въвеждане.

За нас

ALLELCO LIMITED

Прочетете още

Бързо запитване

Моля, изпратете запитване, ние ще отговорим незабавно.

Цифров фазово заключен цикъл (DPLL): Дизайн, компоненти и операции

на 2025/01/7

Еволюцията и въздействието на архитектурата на RISC в съвременните изчисления

на 2025/01/7

Популярни публикации

-

Компютри на сложни инструкции: Как промениха изчисленията?

на 8000/04/18 147760

-

USB-C Pinout и функции

на 2000/04/18 111967

-

Използване на Xilinx Unified Simulation Primitives: Изчерпателно ръководство за FPGA дизайн и симулация

на 1600/04/18 111351

-

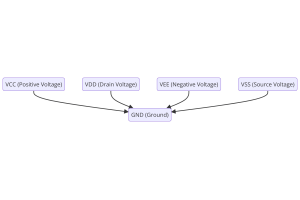

Захранващи напрежения в електрониката: Значение на VCC, VDD, VEE, VSS и GND

на 0400/04/18 83729

-

Ръководство за конектор RJ45: Pinout, окабеляване, видове кабели и употреби

на 1970/01/1 79516

-

Крайното ръководство за цветни кодове в съвременните електрически системи

Начинът, по който нашите електрически системи използват цветове, не е само за външен вид.Всеки цвят на проводника сега показва специфична функция, което улеснява идентифицирането и обработката на е...на 1970/01/1 66930

-

Ръководство за клапа на чист: функция, симптоми, тестване и подмяна на оптимална работа на двигателя

Клапанът на чистката е ключова част от системата на автомобила, която помага да се поддържа чистият въздух, като управлява изпаренията на горивото, преди да могат да избягат в атмосферата.Това не с...на 1970/01/1 63079

-

Качество (Q) Фактор: Уравнения и приложения

Коефициентът на качество, или „Q“, е важен при проверка на това колко добре работят индуктори и резонатори в електронни системи, които използват радиочестоти (RF).'Q' измерва колко добре веригата с...на 1970/01/1 63023

-

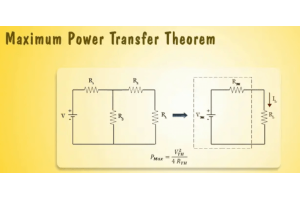

Постигане на пикова ефективност с теоремата за максимален трансфер на мощност

Теоремата за максимален пренос на мощност обяснява как енергия от източник, като батерия или генератор, преминава към свързан товар.Той показва точното състояние, при което товарът получава най -мн...на 1970/01/1 54088

-

Спецификации и съвместимост на батерията A23

Батерията A23 е малка батерия с форма на цилиндър с високо напрежение.Нарича се още 23A, 23AE или MN21, той работи на 12 волта и много по -високо от батериите на AA или AAA.Специалният му ...на 1970/01/1 52160