Изчерпателно ръководство за 74LS74 Dual D Flip-Flop

Тази статия изследва 74LS74 D флип-флоп, ключов компонент в последователните логически системи.Той подчертава функционалността на бистата на IC, конфигурацията на ПИН, оперативните характеристики и разнообразните приложения в цифровата електроника.Ще добиете представа за неговата роля в съхранението на данни, синхронизирането на данни и усъвършенствания дизайн на системата.Каталог

Преглед на 74LS74 D-Type Flip-Flop

The 74LS74 Интегрална схема, двоен ръб, задействан D-Type Flip-Flop, се отличава с поддържането и променянето на данни в цифровите електронни рамки.Той демонстрира адаптивност чрез безпроблемно интегриране с различни схеми като CMOS, TTL и NMOS, отразявайки неговата пригодност за разнообразни електронни пейзажи.Дизайнът на Flip-Flop му позволява да регулира изходите въз основа на логическите нива, заснети при ниски условия за предварително задаване на вход, като показва неговото владеене при анализиране и реагиране на входни сигнали.

Този флип-флоп умело обхваща и запазва D входа през фазите на цикъла на часовника.Той конкретно запазва състоянието на точния положителен ръб на всеки пулс на часовника.Тази прецизност в улавянето е възприета в синхронни системи, където времето повишава работата на системата.Това надеждно улавяне на данни паралел с точността, изисквана от прецизните инструменти в приложенията за време или честота, които изискват непоколебима съгласуваност.

В макро скала може да се направи паралели между функцията на 74LS74 в сложни системи и синхронизацията, необходима за оркестриране на сложни операции.Тук прецизните срокове улесняват кохерентността и оптимизират ефективността.Възможността на Flip-Flop да съхранява сигурно целостта на данните в циклите, обяснява обширната му полезност в различни цифрови приложения, включително съхранение на данни в компютърната памет и среда.

74LS74 ПИН конфигурация

|

Пин № |

ПИН символ |

Име на ПИН |

Описание |

|

5, 9 |

1Q / 2Q |

Изход |

Изходен щифт на джапанката |

|

6, 8 |

1Q '(BAR) / 2Q' (BAR) |

Допълващ изход |

Обърнат изходен щифт на джапанки |

|

3, 11 |

1CLK / 2CLK |

Вход за вход на часовника |

Тези щифтове трябва да бъдат снабдени с пулс на часовника за флип

Флоп |

|

1, 13 |

1Clr (BAR) / 2CLR (BAR) |

Ясни данни |

Възстановява джапанката, като изчисти паметта му |

|

2, 12 |

1d / 2d |

Вход за въвеждане на данни |

Входен щифт на джапанката |

|

4, 10 |

1pre (bar) / 2pre (бар) |

Предварително въвеждане |

Друг входен щифт за джапанки.Също така се нарича a

Задайте щифт |

|

7 |

Vss |

Земята |

Свързани със земята на системата |

|

14 |

VDD/VCC |

Захранващо напрежение |

Захранва ИС обикновено с 5V |

Характеристики на 74LS74

• Работи от 2V до 15V.

• Бързо 40NS Време за преход на сигнала.

• Работи при температури от 0 ° C до 70 ° C.

• Извежда до 8ma за умерени товари.

• Dual D-Type Flip-Flops с биполярни входове и изходи на избутване.

• Ниска употреба на мощност, намалена EMI.

• Идеален за цифрова логика, съхранение на данни и последователни схеми.

• Изисква добро термично управление и правилно заземяване.

Приложения на 74LS74

Регистри за смяна и устройства за управление

В пейзажа на регистрите на Shift 74LS74 оформя сложни времеви последователности, използвани за ефективно управление на потоците от данни.Като осигурява плавен трансфер и синхронизация на данни, той подобрява функционалността на цифровата верига.Неговата точна обработка на данни повишава ефикасността на конвертирането на данни между серийни и паралелни формати.Телекомуникационните дизайни често зависят от тази функция, за да поддържат целостта на данните и прецизността на сигнала.

Памет и буферни вериги

В архитектурата на паметта 74LS74 не само съхранява битовете на данни, но осигурява последователност в процесите.Ролята му като буфер играе роля в изпълнението на задачите за вход-изход, като същевременно запазва целостта на сигнала.Това буфериране е важно за предотвратяване на загубата на данни във високоскоростни изчислителни контексти.

Механизми за фиксиране

Капацитетът на закрепване на 74LS74 му позволява сигурно да запази информация, като има значение в устройствата за задържане на държавата.Тези механизми играят роля в запазването на състоянията на системата по време на цикли на мощност, което позволява на системите да се рестартират точно.В системите за автомобилно управление поддържането на определени състояния предотвратява неизправности и повишава безопасността.

Интеграция в телевизори, компютри и инструменти за работа в мрежа

Той помага при изпълнение на разнообразни логически операции за обработка на сигнали и дисплеи.Мрежовите инструменти печелят от способността на чипа да управляват няколко пътища за данни едновременно, повишавайки пропускателната способност и понижава латентността.

Еквиваленти на 74LS74

• HEF40312B

Използване на IC 74LS74

74LS74 е универсален D-тип джапанки, известен със своето бързо превключване и ниска консумация на мощност, което го прави идеален за синхронни задачи за данни.За да осигурите правилна работа, започнете с потвърждаване, че VCC и GND пиновете са правилно свързани, за да осигурят стабилна мощност.Надеждните мощни връзки са важни за предотвратяване на проблеми, причинени от смущения или нередности в доставката.Входът на часовника, разположен на Пин 3, контролира времето за улавяне на данни.Когато часовникът получи висок сигнал, флип-флоп улавя данни.Сигналите на часовника могат да бъдат получени от микроконтролери (MCU) или таймер 555, в зависимост от нуждите на времето на веригата.

Функционалността на нулиране е друга важна характеристика на 74LS74.Прилагането на висок сигнал към входовете за нулиране изчиства съхранените данни, способност, полезна в системи, изискващи бързо изчистване на данни.Правилното поставяне на линии за нулиране може да оптимизира операциите и да подобри цялостната производителност на системата.За да се подобри по -нататъшното надеждност, е важно да се справят с потенциалните смущения на сигнала чрез ефективни практики за заземяване и стратегически дизайн на веригата.Тези мерки гарантират, че 74LS74 се представя последователно, дори в сложни конфигурации.Можете да увеличите максимално ефективността и надеждността на 74LS74 в дизайна на веригата си.Фигурата по-долу показва интегрираната схема на Flip-Flop 74LS74 D-Type, свързана в конфигурация, която използва своя часовник и нулиране на входовете за управление на състояния на данни, демонстрирайки приложението си в цифрова логическа схема.

74LS74 D-Type Flip-Flop

|

Pre (bar) |

CLR (BAR) |

Clk |

Г |

Q |

Q (BAR) |

|

L |

З |

X |

X |

З |

L |

|

З |

L |

X |

X |

L |

З |

|

L |

L |

X |

X |

З |

З |

|

З |

З |

З |

З |

L |

|

|

З |

З |

L |

L |

З |

|

|

З |

З |

L |

X |

Q₀ |

Q₀ (бар) |

74LS74 Диаграма на връзката

Предимства на D джапанки-джапанки

D Flip-Flops предлагат уникално предимство в дизайна на цифровите вериги чрез отклоняване на едновременни идентични входни състояния.Този аспект играе роля в предотвратяването на сигналните състезания и поддържането на целостта на данните, особено в системите, където времето и секвенирането на повишаване на ефективността.D Flip-Flops гарантират консистенция чрез улавяне само на един вход на цикъл на часовник, като по този начин изглажда потока на данните и минимизирайки потенциалните грешки в метастабилността.За дизайнерите уверената стабилност на потока на данни, предоставена от D Flip-Flops, е надеждна функция за управление на предизвикателствата за времето, които биха могли да компрометират компютърните или мрежовите системи.

Архитектурата на D Flip-Flops осигурява полезност като елементи за забавяне в сложни схеми.Използвайки механизми от затворен затворен, те могат да бъдат коригирани, за да налагат специфични закъснения, управление на разпространението на сигнала с точност.Това умишлено време е от полза за архитектурите на тръбопровода, които изискват данни, за да се преодолеят много етапи предвидимо.Възможността за модулиране на забавянето подпомага проблемите на Skew на часовника, които, ако не бъдат без надзор, биха могли да попречат на производителността на веригата.

Пакет за 74LS74

Заключение

Flip-Flop 74LS74 D-Type е важен за управление на данни с точност в цифровата електроника, като гарантира надеждна синхронизация и съхранение в различни приложения.Неговата гъвкавост и ефективност при обработка и задържане на данни го правят ценен компонент при създаването на стабилни и функционални електронни системи.С капацитета за работа при различни условия, като същевременно поддържа целостта на сигнала, 74LS74 продължава да бъде градивен елемент за усъвършенстване на електронния дизайн и внедряване.Неговата текуща значимост и адаптивност в нови технологични контексти показват значението му в тази област.

За нас

ALLELCO LIMITED

Прочетете още

Бързо запитване

Моля, изпратете запитване, ние ще отговорим незабавно.

често задавани въпроси [FAQ]

1. Колко джапанки в 7474?

Интегралната верига 7474 съдържа две отделни джапанки от тип D, всеки от които е с възможност за откриване на събития на ръба.Този дизайн улеснява ефективното съхранение и преход на цифрови сигнали, като усъвършенства процеса на обработка на данни.Задействането на ръба повишава точността и надеждността, тънкостта, често оценявана чрез практически опит в сложните системи.

2. Какво означава триъгълникът на 74LS74?

В цифровата електроника триъгълникът представлява безпроблемно, подравняващи операциите безпроблемно.В съчетание с него е кръг, обозначаващ активно-ниска сигнализация, която подпомага точните показания на електронната логика.Тези символи са доказали в предотвратяването на погрешно разбрани дизайни, урок, вкоренен в съзнанието на професионалистите за предотвратяване на разбивки на системата.

3. Каква е целта на 74LS74?

Основно 74LS74 съхранява двоични данни, което позволява на потребителите да правят точни промени.Тази адаптивност е особено изгодна за тези в дизайна на системата, където увереността в адаптивността и надеждността на системата е високо ценена, подчертаваща ролята на ИК в сложните изчислителни пейзажи.

4. Какъв е флипният флоп с помощта на 7474?

Активиран чрез преходни преходи, D флип-флоп в рамките на 7474 изравнява Q изходите с граници на вход.Практическият опит показва приноса на този механизъм за стабилно и усъвършенствано управление на данните, за успешното действие на сложните цифрови инфраструктури.

5. Как работи 74LS74N?

74LS74N ангажира своите пинове, което позволява на всеки флип-флоп да работи независимо.Това независимо функциониране е почитано в практически приложения, където модулният дизайн укрепва надеждността и адаптивността на системата, предпочитание често отекна в динамични сценарии.

6. Какви са 4-те типа джапанки?

Има четири основни типа Flip-Flop: Latch/Set-Reseset (SR), JK, T (Toggle) и D (забавяне или данни).Всяка от тях изпълнява специализирана роля в системите за обработка на данни, информирани от различни практически приложения, където усъвършенстването на цифровите процеси има стойност.

7. Каква е разликата между d и t flip-flop?

D Flip-Flops улавя данни, приведени в съответствие със сигналите на часовника, докато T-джапанките разчитат на T входове за превключване на състояния.Тази диференциация се грижи за приложения, изискващи сложни срокове и контрол, където обмисленият подбор и интегриране могат значително да повишат производителността на системата.

8. Каква е таблицата на истината на флоп-флоп?

A D Flip-Flop таблицата за истината ефективно предотвратява едновременното твърдение на входовете S и R, като се използва затворена SR конфигурация с инвертор, за да се представи единствен D вход.В практическия дизайн на схемата тази настройка е умела да предотврати условията на състезанието, общите инженери на препятствия се стремят да преодолеят.

9. Каква е разликата между Latch и Flip Flop?

Flip-Flops са задействани от ръба, за разлика от ключалките, които реагират на промените в нивото на вход.Прихващането на тази разлика е от полза за ефективния дизайн на веригата, тъй като отговаря на уникални нужди от времева точност, постоянна амбиция за оптимизиране на цифровите системи.

Всичко, което трябва да знаете за оперативния усилвател LM358N

на 2024/11/26

TL082 Dual JFET OP-AMP: Pinout, Equivalents и Applications

на 2024/11/26

Популярни публикации

-

Компютри на сложни инструкции: Как промениха изчисленията?

на 8000/04/18 147749

-

USB-C Pinout и функции

на 2000/04/18 111904

-

Използване на Xilinx Unified Simulation Primitives: Изчерпателно ръководство за FPGA дизайн и симулация

на 1600/04/18 111349

-

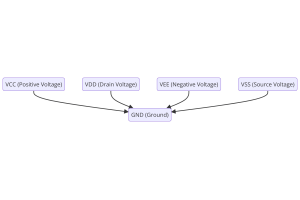

Захранващи напрежения в електрониката: Значение на VCC, VDD, VEE, VSS и GND

на 0400/04/18 83714

-

Ръководство за конектор RJ45: Pinout, окабеляване, видове кабели и употреби

на 1970/01/1 79502

-

Крайното ръководство за цветни кодове в съвременните електрически системи

Начинът, по който нашите електрически системи използват цветове, не е само за външен вид.Всеки цвят на проводника сега показва специфична функция, което улеснява идентифицирането и обработката на е...на 1970/01/1 66867

-

Качество (Q) Фактор: Уравнения и приложения

Коефициентът на качество, или „Q“, е важен при проверка на това колко добре работят индуктори и резонатори в електронни системи, които използват радиочестоти (RF).'Q' измерва колко добре веригата с...на 1970/01/1 63004

-

Ръководство за клапа на чист: функция, симптоми, тестване и подмяна на оптимална работа на двигателя

Клапанът на чистката е ключова част от системата на автомобила, която помага да се поддържа чистият въздух, като управлява изпаренията на горивото, преди да могат да избягат в атмосферата.Това не с...на 1970/01/1 62937

-

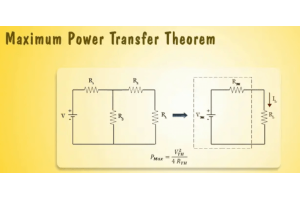

Постигане на пикова ефективност с теоремата за максимален трансфер на мощност

Теоремата за максимален пренос на мощност обяснява как енергия от източник, като батерия или генератор, преминава към свързан товар.Той показва точното състояние, при което товарът получава най -мн...на 1970/01/1 54076

-

Спецификации и съвместимост на батерията A23

Батерията A23 е малка батерия с форма на цилиндър с високо напрежение.Нарича се още 23A, 23AE или MN21, той работи на 12 волта и много по -високо от батериите на AA или AAA.Специалният му ...на 1970/01/1 52087