EP1C4F400C8 FPGA: Характеристики, спецификации, програмиране и алтернативи

Ако работите с програмируема логика, EP1C4F400C8 ви дава практически баланс на ефективност и разходи.В тази статия ще научите какво е тази FPGA, основните му характеристики като логически капацитет, памет и опции за I/O и как структурата му поддържа надежден дизайн.Ще видите и неговите спецификации, приложения в системи, процес на програмиране и как се сравнява с подобни части.Каталог

Какво е EP1C4F400C8?

The EP1C4F400C8 е член на семейството на Cyclone FPGA на Intel (преди това), проектирано като рентабилно и надеждно програмируемо логическо решение.Изградено на процес на SRAM 0,13 µm, това устройство предлага умерена логическа плътност и гъвкави опции за входно/изходно ниво в рамките на компактен пакет FBGA-400.Семейство Cyclone, което включва устройства като EP1C3, EP1C6, EP1C12 и EP1C20, е създадена, за да балансира производителността и достъпността на мащабируемите дизайни, което позволява лесна миграция между нивата на плътността и пакетите.Известен със стабилността и широкото приемане, той остава надежден избор в наследените дизайни.

Търсите EP1C4F400C8?Свържете се с нас, за да проверите текущите запаси, времето за изпълнение и ценообразуването.

EP1C4F400C8 CAD модели

EP1C4F400C8 Символ

EP1C4F400C8 Отпечатък

EP1C4F400C8 3D модел

Функции EP1C4F400C8

• Логическа способност

EP1C4F400C8 предлага около 4000 логически елемента, организирани в 400 логически блока (LABs).Това го прави подходящ за дизайни от среден обхват, които изискват умерена логическа плътност, като същевременно поддържат ефективността на разходите.

• Вградена памет

Той интегрира приблизително 76,5 kbits вградена памет.Тази вътрешна RAM поддържа функции за буфериране на данни, съхранение и малка памет, намалявайки нуждата от компоненти на външната памет в много дизайни.

• Брой с висок I/O

Устройството осигурява 301-конфигурируеми I/O пинове в своя пакет с 400 топки FBGA.Този голям брой на щифтовете позволява богата свързаност за сложни системи, изискващи множество периферни интерфейси.

• Широка поддръжка на стандарти за I/O

Той поддържа множество I/O стандарти, включително LVTTL, LVCMOS, SSTL-2, SSTL-3 и диференциални LVD.Тази гъвкавост позволява на FPGA да взаимодейства директно с различни съвременни семейства на логиката и устройства с памет.

• Високоскоростна диференциална сигнализация

С LVDS поддържат до 640 Mbps, FPGA обработва изискванията за бърз трансфер на данни.Това го прави практичен за приложения като високоскоростни комуникационни връзки и бързи цифрови интерфейси.

• Управление на часовника с PLL

CHIP интегрира две фазови заключени бримки (PLLs) и осем глобални часовници.Тези характеристики позволяват прецизно генериране на часовник, умножение и контрол на трептене за критични за времето приложения.

• Операция на ядрото с ниско напрежение

Работейки при номинално напрежение от 1,5 V ядро, устройството балансира производителността с по -ниска консумация на енергия.Това ниво на напрежение беше оптимизирано за технологията 0,13 µm CMOS, използвана при нейното производство.

• Гъвкави I/O напрежения

FPGA поддържа I/O напрежения от 1,5 V, 1,8 V, 2,5 V и 3,3 V в различни банки.Тази гъвкавост му позволява да взаимодейства както с нас, така и съвременни компоненти на системата.

• Конфигурация, базирана на SRAM

Подобно на други Cyclone FPGA, той е базиран на SRAM и изисква преконфигуриране при всяко захранване.Това осигурява гъвкавост за актуализации, но също така налага външна конфигурационно устройство или контролер.

• Поддръжка за компресия на битстрийм

EP1C4F400C8 поддържа компресиран битстрийм зареждане по време на конфигурация.Това намалява изискванията за външна памет и ускорява времето за конфигуриране.

• PCI съответствие

Тя включва вградена поддръжка за PCI стандарти (33/66 MHz, 32/64-битов).Тази функция позволява на устройството да бъде директно интегрирано в системи, изискващи PCI взаимодействие без допълнителна мостова логика.

Структура на лабораторията на циклона

Диаграмата показва структурата на блока на логическия масив (LAB), използвана в циклона FPGA като EP1C4F400C8.Всяка лаборатория се свързва с мрежа от взаимовръзки: връзки на редове, връзки на колони и локални връзки, които сигнализират на маршрута между логическите елементи и други блокове.Връзките за директни връзки осигуряват бързи пътища с ниска латентност към съседни лаборатории, подобряване на работата на времето в сигналните пътища.Тази архитектура е важна, тъй като балансира гъвкавостта на маршрута с ефективност, което позволява на FPGA да обработва сложни дизайни, като същевременно поддържа оптимизирана скорост и зона.

Диаграма на банките на циклона

Диаграмата илюстрира I/O банковата структура на циклона FPGA като EP1C4F400C8.Устройството е разделено на четири I/O банки, всяка от които се захранва от собствената си шина за захранване, което позволява да се смесват различни стандарти за напрежение в рамките на един FPGA.Всички банки поддържат широк спектър от I/O стандарти, включително LVTTL, LVCMOS, LVDS, RSDS и SSTL, докато банките 1 и 3 също поддържат 3.3-V PCI за съвместимост със наследените системи.Тази гъвкава I/O архитектура е важна, тъй като дава възможност за безпроблемна интеграция с различни външни устройства и интерфейси, което прави FPGA адаптивен към различни приложения.

Спецификации на EP1C4F400C8

|

Тип |

Параметър |

|

Производител |

Altera/intel |

|

Серия |

Cyclone® |

|

Опаковане |

Табла |

|

Статус на част |

Остарял |

|

Брой лаборатории/CLB |

400 |

|

Брой логически елементи/клетки |

4000 |

|

Общи битове на RAM |

78,336 |

|

Брой на I/O. |

301 |

|

Напрежение - захранване |

1.425V ~ 1.575V |

|

Тип монтаж |

Повърхностно монтиране |

|

Работна температура |

0 ° C ~ 85 ° C (TJ) |

|

Пакет / случай |

400-bga |

|

Пакет устройства за доставчици |

400-FBGA (21 × 21) |

|

Основен номер на продукта |

EP1C4 |

Приложения EP1C4F400C8

1. Цифрова обработка на сигнали (DSP)

EP1C4F400C8 може да бъде програмиран за изпълнение на задачи като филтриране, FFT и модулация на сигнала.Неговата комбинация от логически елементи и вградена памет я прави подходящ за високоскоростна обработка.Това му позволява да замени традиционните DSP чипове с гъвкав FPGA разтвор, който може да бъде препрограмиран за различни алгоритми.

2. Вградени и контролни системи

В индустриални и вградени системи тази FPGA често се използва за внедряване на персонализирани контролери, секвенситори и държавни машини.Неговата конфигурируема логика позволява да се приспособи хардуерното поведение именно към нуждите на системата.Чрез интегриране на контролната логика вътре в FPGA броят на външните компоненти се намалява, подобрява надеждността и понижаването на разходите.

3. Преодоляване на комуникация и интерфейс

Устройството поддържа множество I/O стандарти и може да действа като мост между различни комуникационни протоколи.Често се използва за свързване на PCI, LVDS, SDRAM и други интерфейси безпроблемно в рамките на системата.Това го прави много полезен в мрежовото оборудване, вградените контролери и преобразуванията на наследство към модела.

4. Извличане и обработка на данни

С висока наличност на I/O и гъвкава памет, EP1C4F400C8 е добре подходящ за системи за събиране на данни.Той може директно да взаимодейства с ADC и сензори, да обработва данните навреме и да ги подготви за съхранение или предаване.Такива приложения са често срещани при медицински инструменти, тестово оборудване и научни измервателни устройства.

EP1C4F400C8 подобни части

|

Спецификация |

EP1C4F400C8 |

EP1C4F400C8N |

EP1C4F400C8NAA |

EP1C4F400C6N |

EP1C4F324C8N |

EP1C4T144C8N |

|

Производител |

Altera (intel) |

Altera (intel) |

Altera (intel) |

Altera (intel) |

Altera (intel) |

Altera (intel) |

|

FPGA семейство |

Циклон (EP1C4) |

Циклон (EP1C4) |

Циклон (EP1C4) |

Циклон (EP1C4) |

Циклон (EP1C4) |

Циклон (EP1C4) |

|

Логически елементи (LES) |

4000 |

4000 |

4000 |

4000 |

4000 |

4000 |

|

Вградена памет (битове) |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

~ 76,5 kbits |

|

I/O щифтове |

301 |

301 |

301 |

301 |

249 |

97 |

|

Пакет / случай |

400-FBGA |

400-FBGA |

400-FBGA |

400-FBGA |

324-FBGA |

144-TQFP |

|

Степен на скорост |

C8 |

C8 |

C8 |

C6 (по -бързо) |

C8 |

C8 |

|

Основно напрежение |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

|

Работна температура.Обхват |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C.

|

EP1C4F400C8 стъпки за програмиране

Преди да можете да използвате EP1C4F400C8 FPGA, трябва да заредите дизайна си в устройството.Програмирането включва конфигуриране на FPGA с битстрийм файл, така че да знае как да се държи като предвидена верига.

1. Изберете схема за конфигурация и задайте MSEL пинове

Започвате с избора на схемата за конфигуриране, която най -добре отговаря на вашата настройка, като активен сериен, пасивен сериен или JTAG.Това става чрез настройка на MSEL щифтовете на специфични нива на логика преди захранване.Всеки режим използва различни пинове и протоколи, така че трябва да потвърдите съвместимостта с вашите инструменти за проектиране и конфигурационната памет.Извършването на правилния избор тук осигурява плавен процес на конфигуриране.

2. Приложете захранването и инициализирайте устройството

След това захранвайте сърцевината на FPGA и I/O релсите в рамките на определените диапазони на напрежение.По време на стартиране, дръжте NConfig Pin ниско, за да държите устройството в нулиране, докато напрежението на захранването не стаби.След като стабилни, освобождавате нулиране и устройството сигнализира за готовност, като задвижвате щифта NSTATUS.Това гарантира, че FPGA е правилно инициализиран, преди да започне конфигурацията.

3. Предаване на конфигурационния бит поток

На този етап изпращате файла с данни за конфигурация (Bitstream) в FPGA, като използвате избраната от вас схема.В активен сериен или пасивен сериен режим Bitstream идва от външно устройство за памет, докато JTAG позволява директно програмиране чрез кабел.Устройството непрекъснато чете в данните за конфигуриране, докато не приключи.Вашият дизайнерски софтуер генерира този битстрийм, за да съответства на вашите логически изисквания.

4. Потвърдете успешната конфигурация (conf_done)

Когато FPGA приключи зареждането, той отстоява PIN CONF_DONE, за да покаже, че конфигурационните данни са получени успешно.В същото време устройството извършва вътрешна инициализация като регистриране на изчистване и активиране на I/O.Ако conf_done не се повиши, това обикновено означава, че данните за конфигурация или настройка имат грешка.Гледането на този щифт е най -простият начин да се провери, че процесът е завършен.

5. Извършете незадължителна конфигурация в системата

И накрая, имате възможност да актуализирате или препрограмирате FPGA, без да го премахнете от дъската.Използвайки JTAG или вграден контролер, можете да заредите нов битстрийм директно, което е полезно за актуализации на фърмуера.Тази гъвкавост ви позволява да променяте, отстранявате отстраняване на грешки или надграждане на системата си дори след внедряване.Той гарантира, че вашият дизайн, базиран на FPGA, може да се адаптира във времето към променящите се изисквания.

EP1C4F400C8 Предимства и недостатъци

Предимства

• Избор на рентабилния избор за дизайни от среден клас

• Висока броя на I/O в сравнение с подобни устройства за плътност

• Гъвкаво напрежение и стандартна поддръжка на I/O

• Подкрепена от зрели инструменти и документация

• По -ниска употреба на мощността от по -старите поколения на FPGA

Недостатъци

• остарял с ограничена дългосрочна наличност

• По -ниска логика и капацитет на паметта спрямо съвременния FPGAS

• По -бавна работна скорост и производителност на I/O

• Изисква външна памет за конфигурация при захранване

• Липсват усъвършенствани функции като DSP блокове и високоскоростни приемо-предаватели

EP1C4F400C8 Размери на опаковката

|

Тип |

Параметър |

|

Тип пакет |

FBGA (масив с фини стъпки с топка)) |

|

Брой на топката |

400 |

|

Топка стъпка (д) |

1,0 mm (типично за циклона EP1C4F400) |

|

Диаметър на топката (B) |

0,45 mm (номинална) |

|

Размер на пакета (D × E) |

21 mm × 21 mm |

|

Височина на пакета (A) |

2.40 mm (MAX) |

|

Дебелина на субстрата (A2) |

~ 0,40 mm |

|

Дебелина на капачката на плесен (A3) |

~ 1,90 mm |

|

Височина на топката (A1) |

0,25 mm (номинална) |

|

ПИН A1 ъгъл |

Маркиран за ориентация |

|

Оформление на масива |

20 × 20 решетка (с липсващи ъглови топки) |

|

Монтаж |

Повърхностно монтиране (SMD) |

EP1C4F400C8 Производител

EP1C4F400C8 първоначално е произведен от Altera Corporation, пионер в програмируеми логически устройства и FPGA технология.През 2015 г. Altera е придобита от Intel Corporation, и продуктовата линия стана част от програмируемите решения на Intel (PSG).Днес Intel поддържа тези наследствени устройства Altera, като същевременно фокусира развитието върху по -новите FPGA семейства, като гарантира приемственост за съществуващите потребители и подобряване на иновациите в програмируемата логика.

Заключение

EP1C4F400C8 се откроява като рентабилен и универсален FPGA, който предлага солидна производителност за дизайни от среден обхват.Със своите 4000 логически елемента, вградена памет, обширна поддръжка на I/O и съвместимост с множество стандарти за напрежение и интерфейс, той осигурява гъвкавост в различни приложения.Неговата архитектура, процес на програмиране и широка използваемост в DSP, вградени системи и събиране на данни го правят практически избор, въпреки наследствения му статус.Въпреки че му липсват усъвършенствани функции, открити в по-новите устройства и са изправени пред ограничена дългосрочна наличност, той остава надежден вариант, който търси доказани решения в мащабируемите FPGA дизайни.

DataSheet PDF

EP1C4F400C8 таблици с данни:

За нас

ALLELCO LIMITED

Прочетете още

Бързо запитване

Моля, изпратете запитване, ние ще отговорим незабавно.

често задавани въпроси [FAQ]

1. Какви инструменти са необходими за програмиране на EP1C4F400C8?

Нуждаете се от софтуера на Quartus на Intel (преди Altera Quartus II), заедно с поддържан кабел за програмиране като USB-Blaster.Тези инструменти ви позволяват да създадете битстрийма и да го заредите в FPGA.

2. Може ли EP1C4F400C8 да обработва PCI приложения директно?

Да, той има вградено съответствие за PCI стандарти (33/66 MHz, 32/64-битов), което го прави подходящ за системна интеграция, базирана на PCI, без да изисква допълнителна мостова логика.

3. Какво се случва, ако EP1C4F400C8 се провали по време на конфигурация?

Ако конфигурацията се провали, PIN CONF_DONE няма да се отстоява високо.Това обикновено сочи грешка във файла на битстрийм, секвениране на напрежение или настройка на ПИН и трябва да бъде проверено в дизайнерския си поток.

4. Може ли интерфейсът EP1C4F400C8 директно с DDR памет?

Той поддържа няколко I/O стандарта, но няма местни DDR интерфейси като съвременни FPGA.Може да са необходими допълнителни дизайнерски съображения или мостови компоненти.

5. Как EP1C4F400C8 се сравнява с по -новите FPGAs?

В сравнение със съвременните устройства, EP1C4F400C8 има по -ниска скорост, по -малка логическа плътност и по -малко напреднали функции.Въпреки това, той остава рентабилен избор за стабилни, средни дизайни, при които не се изисква авангардна ефективност.

EPM3256AFC256-7 CPLD Преглед: функции, Pinout, програмиране и приложения

на 2025/10/3

ADG432BR Аналогов превключвател IC: Спецификации, Pinout, алтернативи и таблица с данни

на 2025/10/2

Популярни публикации

-

Компютри на сложни инструкции: Как промениха изчисленията?

на 8000/04/18 147776

-

USB-C Pinout и функции

на 2000/04/18 112022

-

Използване на Xilinx Unified Simulation Primitives: Изчерпателно ръководство за FPGA дизайн и симулация

на 1600/04/18 111351

-

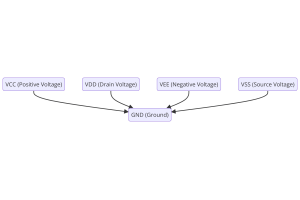

Захранващи напрежения в електрониката: Значение на VCC, VDD, VEE, VSS и GND

на 0400/04/18 83777

-

Ръководство за конектор RJ45: Pinout, окабеляване, видове кабели и употреби

на 1970/01/1 79577

-

Крайното ръководство за цветни кодове в съвременните електрически системи

Начинът, по който нашите електрически системи използват цветове, не е само за външен вид.Всеки цвят на проводника сега показва специфична функция, което улеснява идентифицирането и обработката на е...на 1970/01/1 66964

-

Ръководство за клапа на чист: функция, симптоми, тестване и подмяна на оптимална работа на двигателя

Клапанът на чистката е ключова част от системата на автомобила, която помага да се поддържа чистият въздух, като управлява изпаренията на горивото, преди да могат да избягат в атмосферата.Това не с...на 1970/01/1 63104

-

Качество (Q) Фактор: Уравнения и приложения

Коефициентът на качество, или „Q“, е важен при проверка на това колко добре работят индуктори и резонатори в електронни системи, които използват радиочестоти (RF).'Q' измерва колко добре веригата с...на 1970/01/1 63041

-

Постигане на пикова ефективност с теоремата за максимален трансфер на мощност

Теоремата за максимален пренос на мощност обяснява как енергия от източник, като батерия или генератор, преминава към свързан товар.Той показва точното състояние, при което товарът получава най -мн...на 1970/01/1 54097

-

Спецификации и съвместимост на батерията A23

Батерията A23 е малка батерия с форма на цилиндър с високо напрежение.Нарича се още 23A, 23AE или MN21, той работи на 12 волта и много по -високо от батериите на AA или AAA.Специалният му ...на 1970/01/1 52190