EPM7064STC100-7 CPLD: функции, приложения и ръководство за програмиране в системата

EPM7064STC100-7 е мощен чип от серията Max® 7000S на Intel, предназначен да обработва сложни задачи в електронни устройства.Това ръководство обсъжда основните характеристики и използването на EPM7064STC100-7, като подчертава способността му да бъде препрограмирана лесно, бърза работа и гъвкавия си дизайн.Идеален за много различни технологии, от малки джаджи до големи индустриални машини, този чип е ключова част за изграждането на напреднали цифрови схеми.Каталог

EPM7064STC100-7 Описание

The EPM7064STC100-7 е сложно програмируемо логическо устройство (CPLD) от серията Max® 7000S на Intel.Той има 64 макроклета и 1250 порти, които помагат за изграждането на сложни цифрови схеми.Този чип работи с максимална скорост от 166,7 MHz, със сигнал закъснение от 7,5 наносекунди (NS).Той има 68 входни/изходни (I/O) пина, които работят с 3.3V и 5V логика, което прави лесен за използване в различни вериги.Основна характеристика е неговата 5.0V в системна програмируемост (ISP) чрез JTAG интерфейс (IEEE 1149.1).Това означава, че можете да го препрограмирате, без да го премахвате от веригата, като улесните тестването и актуализациите.Той се предлага в 100-пинов тънък четворен пакет (TQFP), който е компактен, повърхностно монтиран пакет.Този CPLD се използва във вградени системи, дигитална обработка на сигнали, комуникационни устройства и индустриална автоматизация.

Ние предоставяме висококачествени компоненти и персонализирани услуги, така че е най-добре да поставите насипната си поръчка при нас за надеждни CPLD решения.

Функции на EPM7064STC100-7

• Логика с висока плътност: EPM7064STC100-7 е проектиран с 64 макроклета и 1,250 използваеми порти, което го прави много подходящ за внедряване на сложни логически функции в цифровите схеми.Тази архитектура с висока плътност дава възможност за създаване на сложни логически дизайни, като същевременно поддържа ефективност в програмируеми логически операции.Добре оптимизираната структура на макроклетите гарантира ефективно използване на наличните ресурси, подкрепяйки усъвършенствани комбинирани и последователни логически реализации.

• Бързо изпълнение: Изграден за високоскоростна обработка, EPM7064STC100-7 работи с максимална вътрешна честота 166,7 MHz, което позволява бързо изпълнение на логически функции.Забавянето му за разпространение от 7,5 ns осигурява минимална латентност.Тази способност за бързо превключване повишава способността на устройството да обработва високоскоростната обработка на данни, кондиционирането на сигнала и ефективно контролните задачи, което го прави надежден избор за взискателни цифрови системи.

• Универсален I/O: С 68 програмируеми входни/изходни пина, EPM7064STC100-7 предлага изключителна гъвкавост за интеграция в различни дизайни на вериги.Поддържайки както 3,3V, така и 5V логическа нива, тя позволява безпроблемна съвместимост с различни напрежения на системата, като елиминира нуждата от допълнителни превключватели на нивото на напрежение.Тази адаптивност го прави подходящ за приложения в среда със смесено напрежение, като гарантира широка приложимост в вградените системи, индустриалния контрол и комуникационните мрежи.

• Програмируемост в системата (ISP): Едно от предимствата на EPM7064STC100-7 е неговата 5.0V in-System Programmability (ISP), улеснен чрез IEEE STD.1149.1 JTAG интерфейс.Тази функция позволява да се препрограмира и променя логическите функции, без да се обезсърчава или физически премахване на устройството, опростяване на поддръжката, отстраняването на грешки и итеративното развитие.Възможността на ISP намалява престоя и подобрява гъвкавостта на актуализациите на фърмуера, което го прави безценен за динамични и преконфигурируеми цифрови дизайни.

EPM7064STC100-7 CAD модели

SEPM7064STC100-7 Символ

EPM7064STC100-7 отпечатък

EPM7064STC100-7 3D модел

EPM7064STC100-7 Блок-диаграма

The EPM7064STC100-7 Блок-диаграма Показва как логическите елементи на чипа са свързани и контролирани.Той има четири блока за логически масиви (LABs), обозначени с A, B, C и D, всеки от които съдържа 16 макроклета.Тези макрокли изпълняват логически функции и се свързват чрез програмируем масив за свързване (PIA), който позволява гъвкаво маршрутизиране на сигнали.Всяка лаборатория е свързана с контролен блок I/O, обработвайки до 16 входни/изходни щифтове на лаборатория.Диаграмата показва също така глобални контролни сигнали (GCLK1, GCLK2, OE1 и GCLRN), които помагат за управление на функциите на часовника и нулиране на чипа.Някои логически порти обработват тези сигнали, преди да достигнат различни части на системата.Дизайнът на EPM7064STC100-7 позволява да се използва в различни програмируеми логически приложения, като държавни машини, декодиране на адрес и други персонализирани цифрови схеми.Неговите гъвкави взаимовръзки гарантират ефективен поток на сигнала и надеждна работа.

Спецификации на EPM7064STC100-7

|

Тип |

Параметър |

|

Производител |

Altera/intel |

|

Серия |

MAX® 7000S |

|

Опаковане |

Табла |

|

Статус на част |

Остарял |

|

Програмируем тип |

В системния програмируем |

|

Време за забавяне TPD (1) Макс |

7,5 ns |

|

Захранване на напрежението - вътрешно |

4.75V ~ 5.25V |

|

Брой логически елементи/блокове |

4 |

|

Брой макрокли |

64 |

|

Брой порти |

1250 |

|

Брой на I/O. |

68 |

|

Работна температура |

0 ° C ~ 70 ° C (TA) |

|

Тип монтаж |

Повърхностно монтиране |

|

Пакет / случай |

100-TQFP |

|

Пакет устройства за доставчици |

100-TQFP (14x14) |

|

Основен номер на продукта |

EPM7064 |

EPM7064STC100-7 Последователност на програмиране (ISP)

EPM7064STC100-7, част от семейството на CPLD Max 7000S, следва шестстепенна последователност в системата за програмиране (ISP), за да гарантира правилната конфигурация.Този процес ви позволява да програмирате устройството, без да го премахвате от платката.Процесът на ISP включва преместване на инструкции, адреси и данни чрез TDI (тестови данни в) ПИН, докато извличате отговори чрез PIN TDO (Test Data Out).

Първият етап, Въведете ISP, гарантира, че I/O пинове преминават гладко от потребителски режим в режим на ISP и изисква приблизително 1ms.Това е последвано от Проверете идентификатора, където се чете силиконовият идентификатор на устройството, за да се потвърди правилната цел.На следващо място, Насипно изтриване Етапните измествания в инструкциите за изтриване и прилагат импулс от 100 мс, изчистване на всички съществуващи данни в EEPROM клетките.The Програма Следва етап, където адресите и данните се изместват последователно в устройството, прилагайки програмиращи импулси за конфигуриране на EEPROM клетките.Всеки адрес трябва да бъде програмиран индивидуално, като прави тази стъпка отнема време в зависимост от броя на EEPROM клетките в устройството.

След като програмирането приключи, Проверете Етап гарантира, че данните се съхраняват правилно.Тук четените импулси се прилагат към EEPROM клетките и извлечените данни се сравняват с очакваните стойности.Ако се намерят несъответствия, може да е необходимо препрограмиране.И накрая, Излезте от ISP Етап гарантира, че I/O PINS преминава обратно към потребителски режим, изисквайки още 1ms.Общото време за програмиране или проверка се влияе от два основни фактора: време на импулс, необходимо за изтриване на EEPROM, програмиране и операции за четене и време за изместване, което зависи от честотата на TCK (тестов часовник) и броя на циклите, необходими за прехвърляне на инструкции, адреси и данни.Тъй като различните устройства, способни за ISP, имат различен брой клетки на EEPROM, както общите фиксирани, така и променливи времена са уникални за всяко устройство.Общото време на ISP може да се изчисли като функция на честотата на TCK, броя на целевите устройства и EEPROM архитектурата.

Приложения EPM7064STC100-7

Вградени системи

EPM7064STC100-7 се използва широко във вградените системни приложения, където служи като гъвкаво програмируемо логическо решение за контрол на различни периферни устройства, обработка на сигнали и внедряване на персонализирани протоколи.Способността му да взаимодейства с микроконтролери и сензори позволява да се оптимизира производителността на системата, като същевременно поддържа компактен отпечатък.Със своята високоскоростна работа и ниска консумация на енергия е отличен избор за вградени приложения, които изискват надеждност и ефективност.

Обработка на цифрови сигнали (DSP)

При обработката на цифрови сигнали EPM7064STC100-7 играе роля в внедряването на филтри, модулацията на сигнала и различни математически функции.Бързите му скорости на превключване и ниското забавяне на разпространението го правят подходящ за работа с високочестотни задачи за обработка на данни, като се гарантира минимална латентност при преобразуване и манипулиране на сигнала.Обикновено се използва в аудио обработка, телекомуникации и радарни системи.

Комуникации на данни

EPM7064STC100-7 се използва широко в системите за комуникация на мрежи и данни поради способността му да обработва операции с интензивна логика като маршрутизиране на данни, буфериране и корекция на грешки.Неговите програмируеми възможности за I/O му позволяват да се адаптира към различни комуникационни протоколи, което го прави ценен компонент в Ethernet превключватели, рутери и телекомуникационна инфраструктура.Поддръжката му за програмируемост в системата (ISP) също дава възможност за актуализации на полето, подобрявайки адаптивността в динамичните мрежови среди.

Индустриална автоматизация

Промишлените приложения изискват висока надеждност, издръжливост и ниска консумация на енергия, което прави EPM7064STC100-7 предпочитан избор за програмируеми логически контролери (PLC), системи за управление на двигателя и автоматизирано оборудване за тестване.Със своята JTAG базирана в системна програмируемост, той осигурява възможността за усъвършенстване на процесите на автоматизация, без да изисква физическо отстраняване или препроектиране.Неговата гъвкавост в съвместимостта на напрежението също го прави подходящ за взаимодействие с широк спектър от сензори и задвижващи механизми, използвани в индустриални настройки.

EPM7064STC100-7 подобни части

EPM7064STC100-7 предимства

Програмируемост в системата (ISP)

Едно от най-големите предимства на EPM7064STC100-7 е способността му да бъде препрограмирана, докато все още е монтирана в системата.Това елиминира необходимостта от премахване на чипа за актуализации, намаляване на времето за поддръжка и подобряване на ефективността.Можете да внедрите модификации на дизайна, без да прекъсвате производството, което го прави рентабилно решение за дългосрочни проекти.

Високоскоростна производителност

Устройството поддържа висока вътрешна работна честота до 166,7 MHz, което позволява бързо обработка на данни и време за реакция.Това го прави идеален за приложения, изискващи обработка на сигнали, логическо управление и високоскоростно взаимодействие, осигуряване на по-плавно и по-надеждна работа на системата.

Универсална I/O поддръжка

С до 68 конфигурируеми I/O пинове и съвместимост с множество нива на напрежение (3.3V, 5V и толерантни опции за 2.5V, 3.3V и 5V), EPM7064STC100-7 предлага гъвкавост в дизайна на системата.Той позволява безпроблемна интеграция в различни схеми и поддържа среда със смесено напрежение, като намалява проблемите на съвместимостта с други компоненти.

Надеждна работа в средите

Проектиран да функционира в рамките на температурен диапазон от 0 ° C до 70 ° C, EPM7064STC100-7 осигурява последователна и стабилна работа при различни условия.Тази надеждност го прави предпочитан избор за приложения, при които се изисква стабилност на околната среда, като индустриална автоматизация, телекомуникации и вградени системи за управление.

EPM7064STC100-7 Диаграма на пакета

EPM7064STC100-7 е CPLD (сложно програмируемо логическо устройство) от серията Max 7000S на Altera, разположена в 100-пинов тънък четворен плосък пакет (TQFP-100).Този тип пакет е предназначен за приложения на повърхностно монтиране, предлагайки баланс с висока плътност на щифта и компактен размер.The Диаграма за щифтове Следва схема за номериране обратно на часовниковата стрелка, като Пин 1 е разположен в горния ляв ъгъл на пакета.Движейки се обратно на часовниковата стрелка, първите 25 пина заемат лявата страна, щифтове от 26 до 50 са разположени по долния ръб, щифтовете 51 до 75 продължават по дясната страна, а щифтовете 76 до 100 са разпределени по горния ръб.The Пакет TQFP-100 Разполага с тънки проводници, простиращи се навън от четирите страни на плоското, квадратно тяло.Този дизайн повишава съвместимостта на повърхността, като същевременно поддържа адекватно разстояние между щифтовете за лесно запояване и сглобяване.Оловното стъпка (разстояние между съседни пинове) обикновено е 0,5 мм, оптимизира целостта на сигнала, като в същото време свежда до минимум общия отпечатък.

EPM7064STC100-7 Производител

EPM7064STC100-7 е CPLD (сложно програмируемо логическо устройство), първоначално разработено от Altera, полупроводникова компания, известна със своите програмируеми логически решения.През 2015 г., Intel придоби Altera, интегрирайки своите продуктови линии на FPGA и CPLD в програмируемите решения на Intel (PSG).Оттогава EPM7064STC100-7 е маркиран под Intel, въпреки че е отбелязан като остарял.Intel, като производител, поддържаше наследствената поддръжка за CPLDS от серията Max® 7000S, включително този модел, като постепенно насочва фокуса си към съвременни FPGA и програмируеми логически технологии.

Заключение

EPM7064STC100-7 обединява сложни функции, бърза производителност и лесни актуализации в един чип, доказвайки нейната стойност в предизвикателните цифрови настройки.Това ръководство показа как работи, за какво се използва и как се вписва в различни електронни системи.Той помага да накарате устройствата да работят гладко и ефективно, доказвайки, че все още е много полезно за много приложения.Това ръководство предоставя ясен поглед върху това как EPM7064STC100-7 може да помогне ефективно да подобри електронните дизайни и системните операции.

DataSheet PDF

EPM7064STC100-7 таблици с данни:

За нас

ALLELCO LIMITED

Прочетете още

Бързо запитване

Моля, изпратете запитване, ние ще отговорим незабавно.

често задавани въпроси [FAQ]

1. Как 7,5ns забавяне на разпространението на ефективността на въздействието на EPM7064STC100-7?

Забавянето на разпространението 7,5Ns гарантира обработката на сигнала с ниска латентност, което прави този CPLD подходящ за високоскоростни приложения като цифрова обработка на сигнали (DSP), комуникационни системи и индустриална автоматизация, които изискват прецизен контрол на времето.

2. Може ли EPM7064STC100-7 да бъде програмиран с помощта на съвременни инструменти за развитие?

Да, той може да бъде програмиран с помощта на софтуера на Quartus II на Intel (преди Altera Quartus), заедно с подходящ JTAG програмист.Въпреки това, поддръжката за по-стари CPLD като EPM7064STC100-7 може да бъде ограничена в по-новите версии на Quartus, така че може да се наложи да използвате наследени версии като Quartus II 13.0 SP1, които все още поддържат устройства от серията Max® 7000s.

3. Поддържа ли EPM7064STC100-7 средата със смесено напрежение?

Да, тя поддържа както 3,3V, така и 5V логическа нива, което го прави съвместим с широк спектър от цифрови схеми.Тази гъвкавост е полезна за взаимодействие на Legacy 5V компоненти с съвременни 3.3V системи без допълнителна схема за изместване на нивото.

4. Кой е най-добрият метод за отстраняване на неизправности в дизайна на базата на EPM7064STC100-7?

За да отстраните неизправностите, можете да използвате логически анализатор на Quartus Signaltap II или външни осцилоскопи и логически анализатори, за да наблюдавате сигналите.Ако проблемите с програмирането на JTAG за отстраняване на грешки, уверете се, че TDI, TDO, TCK и TMS връзките са правилни и че използвате съвместим USB Blaster или ByteblasterMV програмист.

5. Мога ли да програмирам EPM7064STC100-7, без да го отстранявам от моята платка?

Да.5.0V in-System Programmability (ISP) чрез JTAG (IEEE 1149.1) ви позволява да препрограмирате устройството, докато то остава в системата.Това прави актуализациите на фърмуера, грешката и тестването много по -ефективни в сравнение с традиционните CPLD.

Пълно ръководство за 10K резистор: цветен код, приложения и схема

на 2025/03/10

Кондензатори срещу батерии: Кое е най -доброто за вашите енергийни нужди?

на 2025/03/7

Популярни публикации

-

Компютри на сложни инструкции: Как промениха изчисленията?

на 8000/04/17 147713

-

USB-C Pinout и функции

на 2000/04/17 111743

-

Използване на Xilinx Unified Simulation Primitives: Изчерпателно ръководство за FPGA дизайн и симулация

на 1600/04/17 111324

-

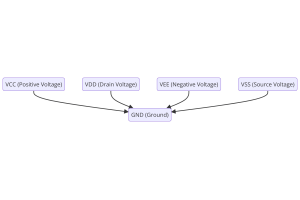

Захранващи напрежения в електрониката: Значение на VCC, VDD, VEE, VSS и GND

на 0400/04/17 83637

-

Ръководство за конектор RJ45: Pinout, окабеляване, видове кабели и употреби

на 1970/01/1 79285

-

Крайното ръководство за цветни кодове в съвременните електрически системи

Начинът, по който нашите електрически системи използват цветове, не е само за външен вид.Всеки цвят на проводника сега показва специфична функция, което улеснява идентифицирането и обработката на е...на 1970/01/1 66789

-

Качество (Q) Фактор: Уравнения и приложения

Коефициентът на качество, или „Q“, е важен при проверка на това колко добре работят индуктори и резонатори в електронни системи, които използват радиочестоти (RF).'Q' измерва колко добре веригата с...на 1970/01/1 62953

-

Ръководство за клапа на чист: функция, симптоми, тестване и подмяна на оптимална работа на двигателя

Клапанът на чистката е ключова част от системата на автомобила, която помага да се поддържа чистият въздух, като управлява изпаренията на горивото, преди да могат да избягат в атмосферата.Това не с...на 1970/01/1 62840

-

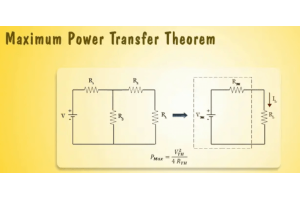

Постигане на пикова ефективност с теоремата за максимален трансфер на мощност

Теоремата за максимален пренос на мощност обяснява как енергия от източник, като батерия или генератор, преминава към свързан товар.Той показва точното състояние, при което товарът получава най -мн...на 1970/01/1 54038

-

Спецификации и съвместимост на батерията A23

Батерията A23 е малка батерия с форма на цилиндър с високо напрежение.Нарича се още 23A, 23AE или MN21, той работи на 12 волта и много по -високо от батериите на AA или AAA.Специалният му ...на 1970/01/1 52010