Ръководство за EPM7256SQC208-10: Функции, Pinout, програмиране, приложения и таблица с данни

Това ръководство е свързано с EPM7256SQC208-10, вид програмируем чип, направен от Intel (първоначално от Altera).Той идва от семейството на Max® 7000s и е известен с това, че е бърз, надежден и лесен за програмиране, докато вече е вътре в устройство.Тази статия обяснява какво прави чипът, как работи, къде се използва и защо е чудесен избор, ако имате нужда от силно и гъвкаво логическо устройство за вашия проект.Каталог

Преглед на EPM7256SQC208-10

The EPM7256SQC208-10 е част от семейството на Max® 7000S на Intel (преди Altera), високоефективен CPLD диапазон, известен със своята стабилна програма за програмиране и оптимизация на логиката.Този модел може да се похвали с около 5000 използваеми порти и включва 256 макрокела, разположени в рамките на 208-пинов пластмасов квадратна плоска пакет (PQFP).Той работи с честота до 128,2 MHz и поддържа 5.0 V работно напрежение, с максимално забавяне на разпространението от 7,5 ns и таван на оперативната температура от +70 ° C.Ключова характеристика е неговата програмируемост в системата чрез вграден IEEE STD.1149.1 JTAG интерфейс, позволяващ динамична конфигурация.Устройствата Max® 7000S са изработени с помощта на Advanced CMOS технология, предлагащи функции като закъснения на логиката на пин-пин до 5 ns и контра честотите, достигащи до 175,4 MHz.Семейството представя разнообразни опции за пакети и е проектирано с програмируеми макроклефни джапанки, които допринасят за значителни икономии на енергия над 50% намаление в някои случаи.Освен това тя включва бит за сигурност за защита на собствените дизайни.

Ако вашата организация се нуждае от солидно програмируемо логическо решение, EPM7256SQC208-10 е надежден избор, така че се свържете с нас днес, за да осигурите вашата насипна поръчка.

EPM7256SQC208-10 CAD модели

SEPM7256SQC208-10 Символ

EPM7256SQC208-10 отпечатък

EPM7256SQC208-10 3D модел

Функции EPM7256SQC208-10

• Висока логическа плътност: EPM7256SQC208-10 осигурява около 5000 използваеми порти и съдържа 256 макроклета.Този висок логически капацитет го прави идеален за прилагане на сложни комбинирани вериги и ефективна логическа интеграция в компактните дизайни.

• Бързо изпълнение: С максимална работна честота от 128,2 MHz и забавяне на разпространението само 7,5 ns, този CPLD осигурява бърза обработка и бързо време за реакция, подходяща за високоскоростни приложения.

• Програмируемост в системата (ISP): Оборудван с IEEE std.1149.1 Интерфейс JTAG, устройството позволява програмиране и тестване в системата, без да е необходимо физическо премахване, улесняване на итеративното развитие и актуализации.

• Разширена архитектура: Използвайки максималната архитектура на второ поколение на Altera и изработена с усъвършенствана CMOS технология, EPM7256SQC208-10 предлага подобрена производителност и издръжливост, като гарантира надеждността в различни оперативни среди.

• Управление на мощността: Устройството разполага с програмируеми режими на пестене на мощност, които могат да намалят консумацията на енергия с над 50% на макрокле, поддържащи енергийно ефективни дизайни и удължаване на живота на батерията в преносимите приложения.

• Функции за сигурност: Програмируем бит за сигурност осигурява защита срещу неоторизиран достъп и копиране на собствени дизайни, като ефективно предпазва интелектуалната собственост.

• Широки работни условия: Работейки при 5.0 V и способен да функционира при температури до +70 ° C, този CPLD се адаптира към различни условия на околната среда, което го прави подходящ както за индустриални, така и за търговски приложения.

• Гъвкави стандарти за I/O : Поддържа Multivolt ™ I/O интерфейсни операции, съвместими както с 3.3 V, така и 5.0 V системи.Тази гъвкавост позволява безпроблемна интеграция със съществуващ и нов хардуер, намалявайки сложността и разходите на системата.

• Поддръжка на дизайна: EPM7256SQC208-10 се поддържа от редица инструменти за проектиране и хардуерни опции за програмиране, опростявайки процеса на разработка и позволява да се съсредоточи върху иновациите, а не върху проблемите на съвместимостта.

EPM7256SQC208-10 Pinout Diagram

Тази диаграма показва оформлението на ПИН за чипа EPM7256SQC208-10 от Altera.Чипът има 208 пина, подредени от четирите страни в квадратна форма.Пин 1 започва в горния ъгъл и числата обикалят чипа в посока обратно на часовниковата стрелка, надолу от лявата страна, за да забият 53, през долната част, за да закрепи 105, нагоре от дясната страна, за да закрепи 157 и обратно към горната десница.Етикетите ви помагат да знаете откъде да започнете и как да поставите чипа правилно на платката.Името в центъра, „EPM7256E / EPM7256S“, означава, че това оформление работи и за двете версии на чип.Тази диаграма е важна при свързване на мощност, сигнали или линии за програмиране към чипа.

EPM7256SQC208-10 Блок-диаграма

Блок-схемата на EPM7256SQC208-10 показва как чипът е организиран за справяне с цифровите логически задачи.Той има четири основни логически блока, наречени Lab A, B, C и D. Всеки блок съдържа 16 макроклета, които са основните строителни части, които вършат логическата работа.Така че в чипа има общо 64 макроклета.Около тези логически блокове са контролни блокове I/O, които свързват чипа към външния свят чрез входни и изходни щифтове.Всеки контролен блок управлява 6 до 16 пина, като оставя сигналите да влизат или извън чипа, ако е необходимо.

В центъра е програмируемият масив за свързване (PIA), който действа като магистрална система, оставяйки сигналите да се движат между логически блокове и I/O пинове.Това ви позволява да насочвате данни по какъвто и да е начин за вашия дизайн.В горната лява част, диаграмата показва някои контролни входове като Global Clock (GCLK), изходните активи (OE) и Clear (GCLR).Тези сигнали помагат да се управлява времето и поведението на логическите вериги през чипа.

Спецификации на EPM7256SQC208-10

|

Тип |

Параметър |

|

Производител |

Altera/intel |

|

Серия |

MAX® 7000S |

|

Опаковане |

Табла |

|

Статус на част |

Остарял |

|

Програмируем тип |

В системния програмируем |

|

Време за забавяне TPD (1) Макс |

10 ns |

|

Захранване на напрежението - вътрешно |

4.75V ~ 5.25V |

|

Брой логически елементи/блокове |

16 |

|

Брой макрокли |

256 |

|

Брой порти |

5000 |

|

Брой на I/O. |

164 |

|

Работна температура |

0 ° C ~ 70 ° C (TA) |

|

Тип монтаж |

Повърхностно монтиране |

|

Пакет / случай |

208-BFQFP |

|

Пакет устройства за доставчици |

208-PQFP (28x28) |

|

Основен номер на продукта |

EPM7256 |

Приложения EPM7256SQC208-10

Индустриална автоматизация

EPM7256SQC208-10 се използва широко в системите за индустриална автоматизация.Неговата висока логическа плътност и бърза ефективност позволяват сложни контролни задачи, които се свързват безпроблемно със сензори и задвижващи механизми.Този CPLD е идеален за повишаване на прецизността и ефективността в производствените линии, системите за контрол на процесите и роботизирани приложения.

Телекомуникации

В телекомуникациите този CPLD превъзхожда управлението на потока на данните и целостта на сигнала в мрежите.Той поддържа функции като преобразуване, маршрутизиране и обработка на сигнали в превключватели и рутери, като гарантира здрави и ефективни комуникационни инфраструктури.

Автомобилни системи

В автомобилната индустрия това устройство допринася за надеждността и усъвършенстването на системи като устройства за управление на двигатели, информационни системи и технологии за подпомагане на водача.Неговата стабилна ефективност при различни условия го прави подходящ за критични за безопасността приложения.

Медицински изделия

Прецизността и програмируемостта на EPM7256SQC208-10 го правят ценен в медицинското оборудване, където са важни точните контролни и надеждни експлоатационни операции.Използва се в устройства за мониторинг на жизнените жизнени условия, управление на диагностичните инструменти и автоматизиране на лечението.

Аерокосмическо и отбрана

В аерокосмическото и отбраната EPM7256SQC208-10 се използва в системи, изискващи високи нива на надеждност и производителност, като сателитни комуникации, навигационни помагала и военна хардуерна контрола.Способността му да работи при екстремни условия е от полза.

Образователни и изследователски институции

Този CPLD също е популярен в образователните условия и изследователски проекти, където неговата препрограмируемост и гъвкавост улесняват експериментирането и обучението в дигиталния дизайн и електрониката.Тя позволява ефективно да прототипира и тества различни логически дизайни.

EPM7256SQC208-10 подобни части

EPM7256SQC208-10 стъпки за програмиране

1. Въведете ISP режим

Тази първоначална стъпка е важна, тъй като преминава CPLD от режим на нормален режим на работа в режим на програмиране в системата (ISP).Това се постига чрез изпращане на конкретна команда чрез JTAG интерфейса.По време на този процес всички I/O пинове на CPLD са три заявени (деактивирани), за да се избегне всякаква намеса или конфликти с други компоненти на веригата.Преходът в ISP режим подготвя устройството за безопасно програмиране и отнема около 1 милисекунда.

2. Проверете идентификационния номер

Веднъж в режим на ISP системата извършва проверка на идентификатор, за да гарантира, че правилното устройство се програмира.Това включва четене на уникалния Silicon ID на устройството чрез интерфейса JTAG.Тази стъпка е добра за проверка, че команди за програмиране и данни ще бъдат изпращани на правилното устройство, предотвратявайки погрешно програмиране и потенциални повреди на устройството.

3. Изтриване на насипно състояние

Преди да могат да бъдат програмирани нови данни, съществуващите данни в CPLD трябва да бъдат изтрити.Стъпката за насипно изтриване ефективно изчиства всички програмируеми клетки в устройството.Това става чрез изместване в инструкцията за изтриване и след това прилагане на 100-милисекусен импулс, който изтрива целия чип.Тази стъпка е важна, за да се гарантира, че остатъците от предишни конфигурации не пречат на новото програмиране.

4. Програма

Тази стъпка включва действителното програмиране на CPLD, където новите данни за конфигурация се записват в устройството.Данните и съответните адреси се изместват в устройството през JTAG интерфейса.Всеки адрес и двойка данни изисква пулс за програмиране, за да се гарантира, че данните са правилно записани в клетките на паметта на CPLD.Тази стъпка се повтаря за всяка точка от данни в картата на паметта на устройството.

5. Проверете

След програмиране, трябва да се провери дали данните са правилно написани на устройството.Тази стъпка за проверка включва четене на програмираните данни от всеки адрес и сравняване с оригиналните входни данни.Тази стъпка гарантира целостта на данните и потвърждава, че процесът на програмиране е успешен без никакви грешки.

6. Излезте от ISP режим

Последната стъпка в процеса на програмиране е да излезете от режима на ISP и да върнете CPLD в нормален работен режим.Това става чрез изпращане на друга команда чрез JTAG интерфейса.При успешен изход I/O пиновете се активират активират и устройството възобновява нормалната функция.Тази стъпка обикновено отнема около 1 милисекунда.

EPM7256SQC208-10 Предимства

Не-променлива конфигурация

EPM7256SQC208-10 използва технологията EEPROM, което му позволява да съхранява конфигурацията си за постоянно.Този нелетен характер означава, че устройството не е необходимо да презареди своите данни за конфигуриране от външна памет всеки път, когато се захранва.Това води до по -бързи времена за стартиране и намалява общата сложност на хардуерния дизайн, като елиминира нуждата от допълнителни компоненти за съхранение на конфигурация.

Програмируемост в системата (ISP)

Една от отличителните характеристики на EPM7256SQC208-10 е неговата поддръжка за програмируемост в системата.Това позволява на устройството да бъде програмирано и препрограмирано, докато е вградено в крайното приложение, без да е необходимо да се отстранява физически.Тази способност опростява актуализациите и модификациите, осигурявайки гъвкавост и лекота на използване по време на развитието и през целия жизнен цикъл на продукта.

Висока броя на I/O и логическата плътност

Устройството предлага значително количество логически ресурси и I/O пинове, с 256 макроклета и 164 потребителски I/O пинове.Този голям брой I/O броя и логическата плътност позволяват интегрирането на множество функции в един чип, улеснявайки по -сложни дизайни, като същевременно запазва пространството на PCB.Това предимство е полезно в приложенията, при които пространството на борда е на първо място и е важно многофункционалността.

Бързо забавяне на щифта към пина

С максимално закъснение с пин до само 10 ns, EPM7256SQC208-10 може да извърши високоскоростни логически операции.Това бързо време за реакция е чудесно в приложения, които изискват възможности за бърза обработка, като високоскоростни комуникации или изчисления, като се гарантира, че системата отговаря на строгите критерии за производителност.

Широко съвместимост на напрежението

EPM7256SQC208-10 е проектиран така, че да бъде гъвкав по отношение на съвместимостта на напрежението, като поддържа вътрешна работа при 5 V и I/O нива при 3.3 V. Тази способност за двойно напрежение позволява на устройството да взаимодейства лесно с 3,3 V и 5 V системи, като намалява нуждата от нивото на напрежението и опростява дизайна на системата.

EPM7256SQC208-10 Размери на опаковане

• Тип пакет: 208-BFQFP (пластмасов четворен плосък пакет)

• Брой щифтове: 208 водещи

• Размер на тялото (L × W): 28 mm × 28 mm

• Монтажен стил: Surface Mount Technology (SMT)

• Оловен терен: Обикновено 0,5 mm между пинове (стандарт за BFQFP)

• Пакетен материал: Пластмаса

• Дебелина на пакета: Приблизително 3,5 мм (варира леко от производителя)

• Топлинни характеристики: Няма изложена подложка;стандартно разсейване на околната среда чрез дъска

• Опаковка на табла: Доставя се в тави за обработка на обем и автоматизация на място

Производител на EPM7256SQC208-10

EPM7256SQC208-10 първоначално е разработен и произведен от Altera Corporation, водещ пионер в програмируеми логически устройства, известни със своята серия CPLD на Max® 7000S.През 2015 г. Altera е придобита от Intel Corporation, един от най -големите производители на полупроводници в света.След придобиването, Intel продължава да поддържа и интегрира CPLD и FPGA технологиите на Altera в своята група за програмируеми решения.EPM7256SQC208-10 представлява наследството на Intel в предлагането на високоефективни, програмируеми логически решения в системата, пригодени за широк спектър от индустриални, телекомуникационни и вградени приложения.Макар и сега класифицирана като остаряла, частта отразява дългогодишния ангажимент на Intel към надеждни и гъвкави програмируеми логически устройства.

Заключение

EPM7256SQC208-10 е интелигентен и надежден чип, който помага да се направят цифровите системи да работят безпроблемно.Той спестява мощност, поддържа различни напрежения и ви позволява да я програмирате, докато вече е инсталиран, което прави актуализациите лесни.Въпреки че сега е по -стар чип, други все още го използват, защото работи добре във всички видове системи.Ако имате нужда от солиден чип за контролиране на логиката във вашия дизайн, този е чудесен вариант.Свържете се с нас днес, ако искате да го поръчате на едро.

DataSheet PDF

EPM7256SQC208-10 таблици с данни:

Софтуерен диск 06/ноември/2020.pdf

Цилиндрични държачи на батерията.pdf

За нас

ALLELCO LIMITED

Прочетете още

Бързо запитване

Моля, изпратете запитване, ние ще отговорим незабавно.

често задавани въпроси [FAQ]

1. Какви инструменти за програмиране са съвместими с EPM7256SQC208-10?

Можете да използвате софтуера Quartus II на Intel (преди Altera Quartus), заедно с JTAG-съвместим програмист като USB-Blaster, за да конфигурирате и програмирате EPM7256SQC208-10 директно в системата.

2. Мога ли да препрограмирам EPM7256SQC208-10 многократно?

Да, EPM7256SQC208-10 поддържа множество цикли на препрограмиране, използвайки своята базирана на EEPROM програмируемост в системата, което го прави идеален за итеративно разработване на дизайн или актуализации след разгръщане.

3. Може ли EPM7256SQC208-10 да се справи с тежки условия на работа?

Той работи надеждно в рамките на търговски температурен диапазон от 0 ° C до +70 ° C, което е достатъчно за повечето индустриални и вградени приложения, макар и не за екстремни или автомобилни среди.

4. Мога ли все пак да програмирам EPM7256SQC208-10, без да го премахна от платката?

Да.CHIP поддържа програмируемост в системата (ISP) чрез JTAG, което ви позволява да го препрограмирате, докато той вече е спорен на вашата дъска, спестявайки време и усилия по време на разработка или поддръжка.

5. Какво прави EPM7256SQC208-10 по-добър от стандартния микроконтролер за логически задачи?

За разлика от микроконтролерите, EPM7256SQC208-10 е CPLD, който се отличава с изпълнение на паралелни логически операции с прецизно време.Идеално е, когато се нуждаете от бърз, детерминиран цифров контрол върху множество сигнали.

Обясниха теоремите на Demorgan: опростяване на логическите изрази за по -добър дизайн на веригата

на 2025/04/25

Примери за основи и вериги на Norton Theorem

на 2025/04/24

Популярни публикации

-

Компютри на сложни инструкции: Как промениха изчисленията?

на 8000/04/18 147768

-

USB-C Pinout и функции

на 2000/04/18 111996

-

Използване на Xilinx Unified Simulation Primitives: Изчерпателно ръководство за FPGA дизайн и симулация

на 1600/04/18 111351

-

Захранващи напрежения в електрониката: Значение на VCC, VDD, VEE, VSS и GND

на 0400/04/18 83764

-

Ръководство за конектор RJ45: Pinout, окабеляване, видове кабели и употреби

на 1970/01/1 79555

-

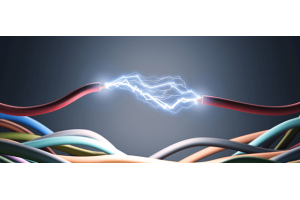

Крайното ръководство за цветни кодове в съвременните електрически системи

Начинът, по който нашите електрически системи използват цветове, не е само за външен вид.Всеки цвят на проводника сега показва специфична функция, което улеснява идентифицирането и обработката на е...на 1970/01/1 66956

-

Ръководство за клапа на чист: функция, симптоми, тестване и подмяна на оптимална работа на двигателя

Клапанът на чистката е ключова част от системата на автомобила, която помага да се поддържа чистият въздух, като управлява изпаренията на горивото, преди да могат да избягат в атмосферата.Това не с...на 1970/01/1 63098

-

Качество (Q) Фактор: Уравнения и приложения

Коефициентът на качество, или „Q“, е важен при проверка на това колко добре работят индуктори и резонатори в електронни системи, които използват радиочестоти (RF).'Q' измерва колко добре веригата с...на 1970/01/1 63029

-

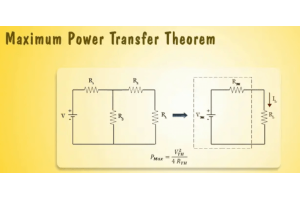

Постигане на пикова ефективност с теоремата за максимален трансфер на мощност

Теоремата за максимален пренос на мощност обяснява как енергия от източник, като батерия или генератор, преминава към свързан товар.Той показва точното състояние, при което товарът получава най -мн...на 1970/01/1 54095

-

Спецификации и съвместимост на батерията A23

Батерията A23 е малка батерия с форма на цилиндър с високо напрежение.Нарича се още 23A, 23AE или MN21, той работи на 12 волта и много по -високо от батериите на AA или AAA.Специалният му ...на 1970/01/1 52176