GAL20V8B-15LJN: Функции, PINOUT, Ръководство за приложения и програмиране

Gal20v8b-15ljn е отлично устройство, предназначено за много цифрови задачи.Това ръководство разглежда отблизо това, което може да направи Gal20V8B-15LJN, като се фокусира върху своята гъвкавост и силна производителност при различни приложения от контролиращи машини до захранване на ежедневните джаджи.Ще покрием основните му функции, как е настроен и как да го програмираме, предлагайки ясен изглед за всеки, който иска да използва разширени логически решения в своите проекти.Каталог

Gal20V8B-15LJN Описание

The GAL20V8B-15LJN От решетъчния полупроводник е отличие в семейството на устройството GAL® 20V8, известна със своята ефективност и високоскоростна работа.Този модел е проектиран с помощта на E2CMOS технология, която се празнува за ниска консумация на енергия, като същевременно поддържа висока производителност.Използвани предимно в цифрови логически приложения, като декодиране на адрес, взаимодействие с устройства и подмяна на логиката, GAL20V8B-15LJN е универсален и подходящ за широк спектър от програмируеми логически приложения.GAL20V8B-15LJN включва конфигурация от 8 макроклета, максимална работна честота от 62,5 MHz и забавяне на разпространението само 15 наносекунди, осигурявайки бързи и надеждни показатели.Той работи на стандартен 5V захранване и се предлага в 28-пинов PLCC (пластмасов оловен чип-носител) пакет.

Ако търсите надеждно и ефективно програмируемо логическо решение, GAL20V8B-15LJN е чудесен избор.Той е изграден за постигане на силна производителност, което го прави интелигентен вариант за бизнеса, който се стреми да надгради технологията си.Ако обмисляте насипна поръчка, това е перфектна възможност да оптимизирате приложенията си и да извлечете максимума от вашата инфраструктура.

GAL20V8B-15LJN ПИН конфигурация

The GAL20V8B-15LJN е a Генерична логика на масива (GAL) Устройство, програмируемо логическо устройство, използвано в различни цифрови логически приложения.The Конфигурация на ПИН следва a Стандартно 24-пинов двоен пакет (DIP) оформление, с ясно дефинирани входове, изходи и контролни щифтове.

На лява страна От диаграмата (PINS 1-12) виждаме предимно входни (I) щифтове, които позволяват на устройството да получава сигнали от външни вериги.Пин 1 и няколко други пина (5, 7, 9 и 11) са обозначени като входове (I).Пин 6 и 22 са маркирани NC (без връзка), което означава, че те не са свързани електрически към вътрешната верига.PIN GND (заземяване) е разположен на щифт 12, като служи като референтно напрежение за устройството.

На дясна страна (PINS 13-24), ние имаме вход/изход (I/O) пинове, които са конфигурируеми като входове или изходи в зависимост от програмираната логика.Тези I/O пинове (18, 19, 21, 23, 25 и 26) осигуряват гъвкава свързаност.ПИНЪТ НА РЕЖИМ (ПИН 15) за дефиниране на работния режим на устройството, а VCC (захранване) щифт на щифт 24 осигурява необходимото напрежение за правилна работа.

В отгоре От устройството има допълнителни контролни сигнали, включително MCLK (главен часовник, щифт 2) и допълнителни NC пинове.Pinout на GAL20V8B позволява ефективен цифров логически дизайн, което го прави широко използван компонент в програмируеми логически схеми.

CAD модели GAL20V8B-15LJN

GAL20V8B-15LJN символ

GAL20V8B-15LJN отпечатък

Функции на Gal20V8B-15LJN

• Забавяне на разпространението: GAL20V8B-15LJN може да се похвали с максимално забавяне на разпространението от 15 наносекунди, което означава, че може да се справи с бързите преходи на сигнала и да работи ефективно в чувствителни към времето приложения.

• Работна честота: Той поддържа максимална работна честота от 62,5 MHz, улеснявайки бързата обработка и отзивчивост в сложни цифрови логически схеми.

• Ниска консумация на енергия: Устройството използва технологията E2CMOS, вариант на CMO, който подчертава енергийната ефективност.Тази технология гарантира, че GAL20V8B-15LJN консумира по-малко мощност, което я прави идеален за приложения, при които е необходима ефективност на мощността, без да се жертва производителността.

• Препрограмируема E2 клетъчна технология: GAL20V8B-15LJN е оборудван с електрически изтриващи се клетки, което позволява препрограмиране и актуализиране на логическите функции, ако е необходимо.Тази функция осигурява отлична гъвкавост и адаптивност при промяна на хардуерните среди или актуализации на системата.

• Универсални изходни логически макрокли: Тя включва 8 изходни логически макроклета, които могат да бъдат програмирани индивидуално за различни логически функции, което позволява да приспособи устройството към специфични нужди.Тези макрокели поддържат конфигурируема изходна полярност и могат да подражават на функционалността на 24-пинови PAL устройства, което прави GAL20V8B-15LJN универсален избор за редица цифрови приложения.

• Подобрена тестичност: Устройството разполага с възможности за предварително зареждане и захранване за всички регистри, осигурявайки 100% функционална тестова способност.Този аспект е чудесен за поддържане на надеждността и предсказуемостта в оперативните настройки, особено когато целостта и производителността на системата са важни.

GAL20V8B-15LJN БЛОГАРКА ДИАГРАМА

Gal20v8b-15ljn е устройство за логика на родовата масива (GAL), което се състои от програмируем и масив (64 x 40), което позволява гъвкава логическа реализация.Блок-схемата показва програмируемия и масив, който служи като основен логически двигател, където сигналите за вход и обратна връзка са логично комбинирани.Тази програмируема матрица позволява да се конфигурира различни комбинирани и последователни логически функции, предлагайки гъвкавост в дизайна на цифровите вериги.

В дясната страна на диаграмата са видими OLMC (изходни логически макро клетки), всяка от които е свързана към изходите и масивите.Тези макро клетки определят поведението на изходните щифтове, независимо дали функционират като комбинирана логика или последователна логика със съхранение на флип-флоп.Освен това, IMUX (входните мултиплексори) позволяват маршрутизиране на вътрешния сигнал, като допълнително подобрява програмируемостта на устройството.I/OQ (входни/изходни пинове) представляват интерфейса между устройството и външните вериги, което позволява двупосочна комуникация в зависимост от конфигурираната логика.

Еквивалентна схема на вход/изход

Еквивалентната схема на вход/изход Gal20V8B-15LJN илюстрира вътрешните електрически характеристики на входните и изходните щифтове на устройството.Тези схеми подчертават как програмируемото логическо устройство (PLD) управлява сигналите чрез защитни вериги, активни издърпвания и механизми за управление на три-държави, като гарантира надеждна работа в цифровите схеми.

The Типичен вход Схемата показва структурата на входен щифт, който включва защитни вериги на ESD (електростатичен разряд), за да се предотврати увреждането от преходни шипове на напрежение.Активната верига за изтегляне гарантира, че щифтът поддържа определено ниво на логика, когато не го задвижва външен сигнал, предотвратявайки плаващи състояния, които биха могли да причинят непредсказуемо поведение.Референтното напрежение (VREF = 3.2V) играе роля при задаване на прага за откриване на логически високи или ниски състояния.

The Типичен изход Схематик илюстрира структурата на изхода, която включва двойка транзистор на бутална була, която позволява силни възможности за задвижване както за високи, така и за ниски логически състояния.Функцията за управление на три състоянието позволява на изходния щифт да въведе състояние с висок импеданс за дизайни, ориентирани към автобус, където множество устройства споделят една и съща връзка.Пътят за обратна връзка осигурява вътрешна връзка обратно към логическия масив, което позволява на устройството да наблюдава или синхронизира изходното състояние с други логически функции.Активната верига за изтегляне осигурява надеждни нива на напрежение, когато е необходимо.

GAL20V8B-15LJN е проектиран за високоскоростни, програмируеми логически приложения с ниска мощност, със здрава защита на входа, гъвкави изходни конфигурации и програмируеми пътища за обратна връзка.Това го прави подходящ за сложни цифрови дизайни, изискващи надеждна цялост на сигнала и конфигурируеми логически операции.

Спецификации на GAL20V8B-15LJN

|

Тип |

Параметър |

|

Производител |

Решетъчна полупроводникова корпорация |

|

Серия |

GAL20V8B |

|

Опаковане |

Тръба |

|

Статус на част |

Остарял |

|

Програмируем тип |

Ee pld |

|

Подкатегория |

Програмируема логика |

|

Брой макрокли |

8 |

|

Максимална работна честота |

62.5 MHz |

|

Забавяне на разпространението - макс |

15 ns |

|

Работно захранващо напрежение |

5 v |

|

Оперативен ток на захранване |

90 ма |

|

Захранващо напрежение - мин |

4.75 v |

|

Захранващо напрежение - макс |

5.25 v |

|

Минимална работна температура |

0 ° C. |

|

Максимална работна температура |

+75 ° C. |

|

Тип монтаж |

Повърхностно монтиране |

|

Пакет / случай |

28-LCC (J-Lead) |

|

Пакет устройства за доставчици |

28-PLCC (11.51x11.51) |

|

Основен номер на продукта |

GAL20V8 |

|

Височина |

3,68 мм |

|

Дължина |

11,5 мм |

|

Ширина |

11,5 мм |

|

Единично тегло |

0,041719 унция |

Приложения на GAL20V8B-15LJN

Вградени системи

Gal20v8b-15ljn често се използва във вградени системи, където персонализираната логика е необходима от специфични функции за контрол.Неговата програмируема природа позволява да адаптира устройството за различни итеративни процеси, подобрявайки функционалността и интеграцията с други компоненти на системата.

Системи за цифрово управление

В системите за цифрово управление този PLD се използва за внедряване на сложна логика за контролиране на двигатели, взаимодействие със сензори и сигнали за обработка.Капацитетът му да обработва подробна логика за управление го прави идеален за приложения, изискващи прецизен оперативен контрол и отзивчивост.

Комуникационни интерфейси

Устройството се отличава с управлението на комуникационните протоколи, кодирането и декодирането на данни и контролирането на държавните машини.Той се адаптира безпроблемно към различни стандарти за комуникация, което го прави универсален избор за телекомуникации и мрежови устройства.

Оборудване за тестване и измерване

За приложения за тестване и измерване, GAL20V8B-15LJN предоставя персонализирани възможности за обработка на данни, маршрутизиране на сигнала и логика на управление.Той дава възможност за разработване на адаптирани измервателни решения, които изискват специфични функции за обработка на данни и контрол.

Автомобилна електроника

В рамките на автомобилния сектор този PLD се откроява поради стабилния си дизайн и отличната защита на електростатичния разряд (ESD).Тези характеристики гарантират надеждна работа при взискателни условия, характерни за автомобилната среда.

Индустриални системи за автоматизация и управление

GAL20V8B-15LJN играе важна роля в индустриалната автоматизация, осигурявайки логиката, необходима за контрол на сложни индустриални процеси и машини.Той дава възможност за автоматизация на задачите и интегрирането на системите за управление, като по този начин повишава ефективността и надеждността в производствените операции.

Потребителска електроника

В потребителската електроника устройството се използва за подобряване на функционалността на домакинските и личните устройства чрез ефективни логически решения.Способността му да изпълнява множество логически функции икономически го прави популярен избор за производителите на потребителски продукти.

Персонализирани държавни машини

PLD е идеален за проектиране на персонализирани държавни машини в цифрови схеми, подобряване на ефективността на контролната логика и оперативното секвениране.Това приложение е чудесно в сценарии, при които са необходими специфични оперативни поведения за ефективно управление на сложни логически задачи.

GAL20V8B-15LJN програмиране

Програмирането на GAL20V8B-15LJN, универсално логическо устройство от решетъчния полупроводник, може да бъде ефективно постигнато в няколко ключови стъпки, използвайки съвместим логически програмист.Първоначално вашата задача е да проектирате логическата схема, която планирате да внедрите.Това се постига чрез използване на език за описание на хардуер (HDL), като CUPL е популярен избор поради своята простота, подходяща за Gal устройства.След като е посочен логическият ви дизайн, следващата стъпка включва съставяне на този дизайн в файл Jedec (.Jed), използващ софтуер като Wincupl.Този файл съдържа необходимата конфигурация, известна като карта за предпазители, за програмиране на GAL.

Действителното програмиране на GAL20V8B-15LJN изисква решетъчен полупроводник одобрен логически програмист, като TL866 е често използван модел поради своята надеждност и лекота на използване.Тази стъпка включва свързване на GAL20V8B-15LJN с програмиста съгласно предоставените инструкции, зареждане на файла JEDEC в софтуера за програмиране и иницииране на цикъла на програмиране.Този цикъл включва автоматично изтриване на всички предишни конфигурации, преди да програмирате новата логика в устройството.И накрая, важна стъпка е проверката на програмираното устройство, като го тества в предвидената верига, за да се гарантира правилно функционира, като завършва процеса на интеграция с вашите специфични изисквания за приложение.

GAL20V8B-15LJN RESET за захранване

Схемата за нулиране на захранването в GAL20V8B-15LJN гарантира, че всички вътрешни регистри се инициализират в известно състояние по време на стартиране на системата.Тъй като мощността се прилага, VCC напрежението трябва да се издигне монотонно без колебания, за да се предотврати нередовно поведение.След като VCC достигне своето минимално необходимо ниво, вътрешните регистри ще се нулират в рамките на максимално закъснение от 1 μs (TPR), като задават всички Q изходи на логика 0. Ако регистрираните изходни щифтове са активирани, те ще бъдат по подразбиране на логиката 1, независимо от програмираните им програмираниполярност.Това гарантира предвидима инициализация, опростявайки дизайна на държавните машини и последователните логически схеми.

За да се осигури валидно нулиране, входът на часовника (CLK) трябва да се държи на статично ниво на TTL по време на захранване.Устройството не трябва да бъде с часовник, докато не бъдат изпълнени всички времена за настройка на пътя за въвеждане и обратна връзка, както е показано на диаграмата.Часовникът трябва да отговаря на изискванията за минимална ширина на импулса, преди да започне нормалната работа.Поддържайки тези условия, механизмът за нулиране на захранването гарантира, че логическото устройство започва в стабилно и добре дефинирано състояние, предотвратявайки непредвидени преходи или проблеми с метастабилността в цифровите схеми.

GAL20V8B-15LJN подобни части

GAL20V8B-15LJN предимства

Подобрена гъвкавост на дизайна

Gal20v8b-15ljn е проектиран с универсална архитектура, която позволява на макроклетите на изходната логика (OLMC) да бъдат конфигурирани от потребителя.Тази гъвкавост поддържа широк спектър от приложения и персонализиране, което позволява да се оптимизира логическото устройство за специфични задачи и функции без ограниченията, свързани с по -малко гъвкави дизайни.

Намалена консумация на енергия

Използвайки Ultramos® Advanced CMOS технология, GAL20V8B-15LJN намалява консумацията на енергия с 50% до 75% в сравнение с традиционните биполярни логически устройства.Това го прави екологична опция, която също свежда до минимум топлинния изход и подобрява дълголетието на устройството.Типичните токове на захранване са значително по-ниски, със 75 mA за стандартни версии с ниска мощност и дори по-ниски при 45 mA за версии на четвърт мощност, като гарантират енергийната ефективност в среди с високо търсене.

Здрава защита на ESD

Това устройство включва силни електростатични механизми за защита от разряд (ESD), за поддържане на оперативната стабилност и надеждността в среди, предразположени към статично изхвърляне.Подобна защита е добра в индустрии като автомобилна и индустриална автоматизация, където електронните компоненти могат да бъдат подложени на строги условия и където ESD може иначе да доведе до повреда на устройството или нередовно поведение.

GAL20V8B-15LJN Производител

Semiconductor Corporation на решетката е световен лидер в Smart Connectivity Solutions.Известна със своите програмируеми логически устройства с ниска мощност, решетката се грижи предимно за потребителите, комуникациите и индустриалните пазари.Иновативната продуктова гама на компанията включва FPGAS (полеви програмируеми масиви на портата), CPLD (сложни програмируеми логически устройства) и устройства за управление на захранването, които са неразделна част от интелигентните приложения, които изискват бързи отговори.Решеят полупроводник се отличава на конкурентния технологичен пазар с фокуса си върху решения с ниска мощност, малки размери и високоефективни решения.Тези атрибути правят продуктите му идеални за активиране на технологии в области като мрежова инфраструктура, крайни изчисления и интелигентни IoT устройства.Lattice изгради репутация за предоставяне на персонализирани решения, които отговарят на специфични нужди, поддържани от цялостни софтуерни инструменти и среди за разработка, които оптимизират дизайна и внедряването на продукта.

Заключение

Gal20v8b-15ljn от решетъчния полупроводник е първокласно устройство, което отговаря на взискателните нужди на съвременните цифрови системи с бързото си производителност, енергийно спестяващ дизайн и многостранни опции за програмиране.Това устройство е изградено за справяне със сложни предизвикателства в широк спектър от настройки, от големи индустриални системи до лична електроника, което го прави солиден избор за изграждане на модерни цифрови решения.Това ръководство обясни техническите детайли и предимствата на GAL20V8B-15LJN, както и как може да се използва в различни области, показвайки нейното значение за подобряване на цифровите настройки навсякъде.

DataSheet PDF

GAL20V8B-15LJN таблици с данни:

За нас

ALLELCO LIMITED

Прочетете още

Бързо запитване

Моля, изпратете запитване, ние ще отговорим незабавно.

често задавани въпроси [FAQ]

1. Може ли GAL20V8B-15LJN да бъде програмиран да поддържа наследени системи?

Да.Gal20v8b-15ljn е проектиран с гъвкавост, който може да бъде програмиран да взаимодейства както със съвременни, така и със наследени системи.Неговата програмируема логика позволява широк спектър от персонализирани конфигурации, които могат да бъдат пригодени да отговарят на конкретни наследствени изисквания.

2. Какви инструменти за програмиране и софтуер са съвместими с GAL20V8B-15LJN?

Gal20V8B-15LJN е съвместим с редица инструменти за програмиране и софтуер, включително Wincupl, Lattice Diamond и инструменти на трети страни, които поддържат JEDEC файлове.Тази съвместимост осигурява безпроблемна интеграция във вашите съществуващи работни процеси за развитие.

3. Как GAL20V8B-15LJN се справя с колебанията и скованията на мощността?

GAL20V8B-15LJN е изграден със стабилни функции за управление на захранването, които предпазват от колебания и скокове, осигурявайки стабилна работа дори в среди с нестабилни захранвания.

4. Може ли GAL20V8B-15LJN да се използва във високотемпературна среда?

Да, Gal20v8b-15ljn е проектиран да работи ефективно в широк диапазон от температури.Високата му термична стабилност го прави подходящ за използване във високотемпературни индустриални среди, без да се компрометира производителността.

5. Кои са най-често срещаните приложения на GAL20V8B-15LJN в индустриални настройки?

В индустриалните настройки Gal20V8B-15LJN обикновено се използва за машинно управление, автоматизирано тестово оборудване и мониторинг на системата поради надеждната си производителност и универсалната програмируемост.

LFXP2-8E-5QN208C FPGA: Еквиваленти, функции, приложения и предимства

на 2025/02/11

Как резисторът на двигателя на вентилатора контролира въздушния поток на колата ви

на 2025/02/11

Популярни публикации

-

Компютри на сложни инструкции: Как промениха изчисленията?

на 8000/04/18 147770

-

USB-C Pinout и функции

на 2000/04/18 112006

-

Използване на Xilinx Unified Simulation Primitives: Изчерпателно ръководство за FPGA дизайн и симулация

на 1600/04/18 111351

-

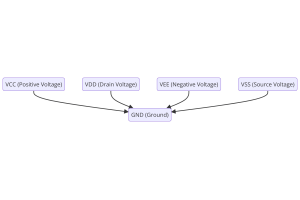

Захранващи напрежения в електрониката: Значение на VCC, VDD, VEE, VSS и GND

на 0400/04/18 83768

-

Ръководство за конектор RJ45: Pinout, окабеляване, видове кабели и употреби

на 1970/01/1 79564

-

Крайното ръководство за цветни кодове в съвременните електрически системи

Начинът, по който нашите електрически системи използват цветове, не е само за външен вид.Всеки цвят на проводника сега показва специфична функция, което улеснява идентифицирането и обработката на е...на 1970/01/1 66959

-

Ръководство за клапа на чист: функция, симптоми, тестване и подмяна на оптимална работа на двигателя

Клапанът на чистката е ключова част от системата на автомобила, която помага да се поддържа чистият въздух, като управлява изпаренията на горивото, преди да могат да избягат в атмосферата.Това не с...на 1970/01/1 63098

-

Качество (Q) Фактор: Уравнения и приложения

Коефициентът на качество, или „Q“, е важен при проверка на това колко добре работят индуктори и резонатори в електронни системи, които използват радиочестоти (RF).'Q' измерва колко добре веригата с...на 1970/01/1 63040

-

Постигане на пикова ефективност с теоремата за максимален трансфер на мощност

Теоремата за максимален пренос на мощност обяснява как енергия от източник, като батерия или генератор, преминава към свързан товар.Той показва точното състояние, при което товарът получава най -мн...на 1970/01/1 54096

-

Спецификации и съвместимост на батерията A23

Батерията A23 е малка батерия с форма на цилиндър с високо напрежение.Нарича се още 23A, 23AE или MN21, той работи на 12 волта и много по -високо от батериите на AA или AAA.Специалният му ...на 1970/01/1 52184