Разбиране на LFSC3GA25E-7F900C FPGA архитектура и ключови функции

Изследването на LFSC3GA25E-7F900C ви дава по-отблизо как програмируемите логически устройства поддържат гъвкави цифрови системи.Можете да използвате тази FPGA, за да организирате пътища за данни, да управлявате сигнали и да изграждате персонализирани логически функции в един чип.Вътрешното му оформление съчетава програмируеми логически клетки, блокове памет и входни изходни банки, така че сигналите да се движат ефективно през устройството.Разбирането как тези секции работят заедно ви помага да видите колко сложни електронни системи са структурирани.От комуникационен хардуер до системи за управление, този FPGA предлага практичен начин за създаване на адаптивни цифрови проекти.Каталог

LFSC3GA25E-7F900C Преглед

LFSC3GA25E-7F900C е програмируемо логическо устройство, предназначено да поддържа конфигурируеми цифрови функции във вградени електронни системи.Устройството съдържа базирана на мрежа логическа структура с хиляди програмируеми елементи, вътрешни ресурси на паметта и множество входни и изходни връзки за външна комуникация.Архитектурата му позволява цифрови схеми, пътища за управление и задачи за обработка на сигнали да бъдат реализирани в рамките на един чип.Интегрираните мрежи за маршрутизиране свързват логически блокове и секции на паметта, така че данните да могат да се движат през устройството по структуриран начин.Работата се поддържа от нисък диапазон на захранване на ядрото и пакет с висок брой пинове, подходящ за гъсто оформление на платки.

Търся LFSC3GA25E-7F900C.Свържете се с нас, за да проверите текущите наличности, времето за изпълнение и цените.

Банки на LFSC3GA25E-7F900C

Подредбата на входната и изходната банка, използвана в LFSC3GA25E-7F900C FPGA, показваща как устройството организира своите програмируеми входно-изходни ресурси в множество региони с контролирано напрежение.Осем банки са разпределени около периметъра на устройството и всяка банка включва групирани връзки за VCCIO захранване, входове за референтно напрежение, означени с VREF, щифтове за крайно напрежение, означени с VTT, и земя.Тази структура позволява на всяка банка да работи с независими електрически условия, така че различни стандарти на сигнала да могат да се поддържат от отделни страни на устройството.Интерфейсните блокове на SERDES се появяват близо до горните банки, за да поддържат високоскоростни серийни комуникационни канали, свързани към близки I O региони.Оформлението също така идентифицира споделени референтни щифтове и захранващи връзки, които определят как външните сигнали взаимодействат с вътрешната програмируема логика чрез банковата I O структура.

LFSC3GA25E-7F900C CAD модел

LFSC3GA25E-7F900C Символ

LFSC3GA25E-7F900C Отпечатък

LFSC3GA25E-7F900C 3D модел

Характеристики на LFSC3GA25E-7F900C

Програмируема логика с висока плътност

Устройството интегрира около двадесет и пет хиляди програмируеми логически елемента, подредени в организирана мрежа.Тези логически клетки могат да бъдат конфигурирани да прилагат цифрови пътеки за управление, комбинирана логика и аритметични операции в рамките на вградени системи.

Архитектура на вградената памет

Ресурсите на вътрешната памет осигуряват повече от един мегабит капацитет за съхранение за буфериране на данни и поддръжка на логически операции.Тези блокове памет са разпределени в цялото устройство, така че логическите схеми да имат локален достъп до данните без дълги пътища за маршрутизиране.

Гъвкава входна и изходна свързаност

До триста седемдесет и осем входни и изходни връзки позволяват на устройството да взаимодейства със сензори, комуникационни интерфейси и други цифрови компоненти.Пин структурата поддържа множество електрически стандарти в независими I O банки.

Интегрирани ресурси за управление на часовника

Вътрешните блокове за управление на часовника помагат за разпределянето на синхронизиращите сигнали в програмируемата логическа структура.Тези ресурси поддържат синхронизирано време на сигнала, така че цифровите операции да се извършват в подредена и предвидима последователност.

Възможност за високоскоростен сериен интерфейс

Специализирани блокове за сериен интерфейс поддържат високоскоростни комуникационни канали за пренос на данни между системните модули.Тези блокове се свързват с близки I O банки и спомагат за поддържането на стабилно предаване на сигнала в интензивни дизайни на данни.

Блокове за структурирана логическа обработка

Специализирани вътрешни блокове за обработка разширяват логическата структура и позволяват на дизайнерите да прилагат по-ефективно повтарящи се цифрови структури.Тази подредба поддържа задачи като обработка на пакети, контролна последователност и паралелни операции с данни.

Програмируема мрежа за маршрутизиране

Структурирана мрежа за маршрутизиране свързва логически клетки, блокове памет и интерфейсни изводи.Сигналите могат да преминават през мрежата по множество пътища, което позволява на дизайнерите да организират цифрови функции по начини, които съответстват на системната архитектура.

Интегриране на пакет за повърхностен монтаж

Устройството се помещава в пакет с масивна решетка с голяма топка, който поддържа плътна интеграция на платка.Тази структура на пакета позволява много електрически връзки да бъдат подредени в компактен отпечатък за усъвършенствани електронни модули.

LFSC3GA25E-7F900C Технически спецификации

| Атрибут на продукта | Стойност на атрибута |

| производител | Решетъчен полупроводник |

| Напрежение - Захранване | 0,95V ~ 1,26V |

| Общо RAM битове | 1966080 |

| Пакет устройства на доставчика | 900-FPBGA (31x31) |

| Серия | SC |

| Опаковка / Калъф | 900-BBGA |

| Пакет | поднос |

| Работна температура | 0°C ~ 85°C (TJ) |

| Брой логически елементи/клетки | 25 000 |

| Брой LAB/CLB | 6250 |

| Брой I/O | 378 |

| Тип монтаж | Повърхностен монтаж |

| Основен номер на продукта | LFSC3GA25 |

| Състояние на RoHS | RoHS несъвместим |

| Ниво на чувствителност към влага (MSL) | 3 (168 часа) |

| Състояние на REACH | REACH Незасегнати |

| ECCN | 3A991D |

| HTSUS | 8542.39.0001 |

Опростена блокова схема на LFSC3GA25E-7F900C

Базирано на мрежа вътрешно оформление на LFSC3GA25E-7F900C FPGA, показващо разположението на програмируема логика, блокове памет, часовникови ресурси и високоскоростни интерфейсни структури.Програмируемите функционални единици образуват централната логическа структура, където се изпълняват конфигурируеми цифрови схеми.Разпределените вградени блокови RAM секции на sysMEM осигуряват вътрешно съхранение на данни и буфериране в рамките на логическия масив.Програмируемите входно-изходни клетки, разположени по краищата на устройството, свързват вътрешната логика с външни щифтове, като всеки програмируем входно-изходен клъстер съдържа множество програмируеми входно-изходни връзки.Четворните блокове SERDES и интерфейсите на физическия подслой на кодиране се появяват близо до горните региони, за да поддържат високоскоростна серийна комуникация.Структурираните ASIC блокове, обозначени с MACO, са интегрирани в логическата тъкан, за да поддържат специализирани структури за обработка.Ресурсите за управление на часовника, означени с sysCLOCK analog PLLs и sysCLOCK DLLs, се поставят в краищата на оформлението, за да генерират и разпространяват сигнали за синхронизиране в програмируемата архитектура.

Диаграма на срез на LFSC3GA25E-7F900C

Вътрешна структура на логически срез, използван в рамките на програмируемия функционален блок на LFSC3GA25E-7F900C FPGA.Два блока LUT4 изпълняват комбинирани логически операции, използвайки четири входни сигнала, означени с A, B, C и D. Интегрираната логика за пренасяне поддържа аритметични операции чрез свързване на входни и изходни сигнали за пренасяне между съседни срезове.Елементите с тригер или ключалка съхраняват изходни данни от логическото стъпало, създавайки регистрирани изходи, обозначени с Q0 и Q1.Контролни входове като часовник, активиране на часовник и сигнали за настройка или нулиране регулират последователната работа на елементите за съхранение.Връзките за маршрутизиране на левия и десния ръб свързват среза със заобикалящата програмируема мрежа за свързване, позволявайки на сигналите да влизат от ресурсите за маршрутизиране и да връщат обработените изходи обратно към тъканта за маршрутизиране.

Приложения на LFSC3GA25E-7F900C

Индустриални системи за управление

Програмируемите логически ресурси позволяват на устройството да управлява времеви последователности, маршрутизиране на сигнала и задачи за цифрово управление в автоматизирано оборудване.Той може да координира множество сензори и изпълнителни механизми, като същевременно поддържа стабилна цифрова обработка в системата за управление.

Инфраструктура за комуникация на данни

Комуникационното оборудване често изисква гъвкава цифрова обработка за обработка на данни и контрол на интерфейса.Устройството може да обработва входящи потоци от данни, да организира логиката на маршрутизиране и да поддържа комуникационни връзки в мрежовия хардуер.

Вградени компютърни платформи

Вградените системи използват програмируема логика за управление на потока от данни между процесори, памет и интерфейсни устройства.Устройството може да реализира персонализирани цифрови пътеки, които адаптират поведението на системата към конкретни изисквания на приложението.

Високоскоростни системи за събиране на данни

Системите за измерване често събират сигнали от множество източници едновременно.Програмируемата логическа структура може да организира входящите цифрови сигнали, да синхронизира времето и да подготви данните за по-нататъшна обработка или прехвърляне.

Хардуер за обработка на сигнали

Устройството може да изпълнява конфигурируеми аритметични и логически операции, които поддържат функции за обработка на сигнали.Цифровите филтри, контролните вериги и задачите за преобразуване на данни могат да бъдат реализирани директно в рамките на програмируемата логическа структура.

LFSC3GA25E-7F900C Предимства и недостатъци

Предимства

• Големият програмируем логически капацитет поддържа сложни цифрови функции

• Големият брой входни и изходни връзки позволява гъвкава системна интеграция

• Вградените блокове памет осигуряват вътрешно съхранение на данни и буфериране

• Реконфигурируема логическа структура позволява хардуерните функции да бъдат актуализирани чрез промени в дизайна

• Множество I O банки позволяват различни стандарти на сигнала в едно устройство

Недостатъци

• Процесът на проектиране изисква специализирани инструменти за разработка и работни процеси за конфигуриране

• Сложността на устройството може да увеличи времето за проектиране на системата по време на разработката

• Големият размер на опаковката изисква внимателно оформление на печатната платка

• Управлението на захранването трябва да се има предвид, когато са активни много логически ресурси

LFSC3GA25E-7F900C Алтернативи

| Номер на част | производител | Ключови характеристики | Случай на употреба/Бележки |

| LFSC3GA25E-7FFN1020C | Lattice Semiconductor Corporation | FPGA устройство от фамилията SC, предлагащо около 25 000 логически елемента, вградени ресурси на паметта и голям брой програмируеми I/O пинове.Той използва BGA пакет с фина стъпка, който поддържа гъсто оформление на вериги и сложни цифрови дизайни. | Използва се във вградени системи за управление, комуникационни интерфейси и индустриална електроника, където са необходими програмируем хардуер и висока I/O свързаност. |

| LFSC3GA25E-7FFA1020C | Lattice Semiconductor Corporation | Програмируема FPGA с подобни логически ресурси в серията LFSC3GA25E.Осигурява конфигурируеми логически блокове, вградена памет и гъвкаво цифрово маршрутизиране, което позволява на дизайнерите да прилагат персонализирани цифрови схеми. | Подходящ за цифрова обработка на сигнали, свързване на интерфейси и програмируем хардуерен контрол във вградена електроника и комуникационни системи. |

| LFSC3GA25E-6FN900C | Lattice Semiconductor Corporation | FPGA устройство с около 25K логически елемента и интегрирани блокове памет, проектирано за програмируем цифров хардуер.Пакетът предоставя много I/O връзки, които поддържат сложна системна интеграция. | Често се използва в индустриални системи за управление, вградени компютърни платформи и мрежово оборудване, което изисква гъвкава хардуерна конфигурация. |

Относно решетъчния полупроводник

Lattice Semiconductor е компания за полупроводници, основана през 1983 г. и със седалище в Хилсбъро Орегон в Съединените щати.Компанията разработва програмируеми логически устройства и свързаните с тях технологии, използвани в компютрите, комуникациите, индустриалните системи и потребителската електроника.Неговите продуктови линии включват полеви програмируеми гейт масиви, програмируеми логически устройства и интерфейсни решения, проектирани да поддържат гъвкав дизайн на цифрова система.Решетъчните устройства се използват широко във вградени системи, където програмируемите хардуерни функции помагат за управление на обработката на данни, контролната логика и маршрутизирането на сигнала в рамките на компактни електронни платформи.

Заключение

LFSC3GA25E-7F900C FPGA съчетава програмируема логика, вградена памет и гъвкави входно-изходни връзки в едно устройство.Като разберете неговата архитектура, можете да видите как са организирани цифровите логически функции и как сигналите преминават през програмируемата тъкан.Функции като конфигурируеми логически елементи, мрежи за маршрутизиране и блокове за управление на часовника позволяват на устройството да поддържа много системни дизайни.Структурата му го прави подходящ за обработка на данни, контролна логика и комуникационен хардуер.Когато изследвате диаграмите и спецификациите, получавате по-ясна картина за това как програмируемият хардуер поддържа адаптивни електронни системи.

PDF лист с данни

LFSC3GA25E-7F900C Лист с данни:

All Dev Pkg Mark Chg 12/Nov/2018.pdf

За нас

ALLELCO LIMITED

Прочетете още

Бързо запитване

Моля, изпратете запитване, ние ще отговорим незабавно.

често задавани въпроси [FAQ]

1. Какъв тип устройство е LFSC3GA25E-7F900C?

LFSC3GA25E-7F900C е полево програмируем гейт масив или FPGA, който позволява цифровите логически схеми да бъдат конфигурирани чрез хардуер програмиране.Съдържа програмируеми логически блокове, ресурси за маршрутизиране, и елементи на паметта в един чип.

2. Какви са логическите елементи в LFSC3GA25E-7F900C FPGA?

Логическите елементи са малки програмируеми единици вътре в FPGA, които извършва цифрови операции като логически сравнения, аритметика задачи и обработка на сигнали.Хиляди от тези елементи работят заедно за създаване на персонализирани хардуерни функции.

3. Как работят I O банките в тази FPGA?

Входно-изходните банки групират набори от щифтове, които споделят мощност и справка напрежения.Всяка банка може да поддържа различни електрически стандарти, които позволява сигнали от множество интерфейси да се свързват към едно и също устройство.

4. Каква е целта на вградената памет в устройството?

Вградените блокове памет съхраняват данни в рамките на FPGA, така че логическите схеми имат бърз достъп до информация.Тези блокове се използват за буфериране данни, временно съхранение и поддържащи задачи за обработка на сигнали.

5. Къде обикновено се използва LFSC3GA25E-7F900C?

Този FPGA се използва обикновено в комуникационни системи, индустриални хардуер за управление, цифрово оборудване за обработка на сигнали и вградени електронни платформи, където е необходима програмируема цифрова логика.

Какво прави EPF8282AVTC100-4 FPGA в цифровите системи

на 2026/03/10

Какво е H7 батерия?Размер, характеристики и използване на превозното средство

на 2026/03/10

Популярни публикации

-

Компютри на сложни инструкции: Как промениха изчисленията?

на 8000/04/18 147774

-

USB-C Pinout и функции

на 2000/04/18 112011

-

Използване на Xilinx Unified Simulation Primitives: Изчерпателно ръководство за FPGA дизайн и симулация

на 1600/04/18 111351

-

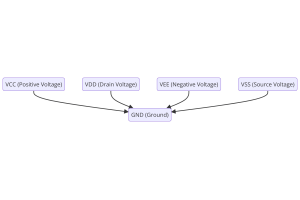

Захранващи напрежения в електрониката: Значение на VCC, VDD, VEE, VSS и GND

на 0400/04/18 83769

-

Ръководство за конектор RJ45: Pinout, окабеляване, видове кабели и употреби

на 1970/01/1 79565

-

Крайното ръководство за цветни кодове в съвременните електрически системи

Начинът, по който нашите електрически системи използват цветове, не е само за външен вид.Всеки цвят на проводника сега показва специфична функция, което улеснява идентифицирането и обработката на е...на 1970/01/1 66960

-

Ръководство за клапа на чист: функция, симптоми, тестване и подмяна на оптимална работа на двигателя

Клапанът на чистката е ключова част от системата на автомобила, която помага да се поддържа чистият въздух, като управлява изпаренията на горивото, преди да могат да избягат в атмосферата.Това не с...на 1970/01/1 63100

-

Качество (Q) Фактор: Уравнения и приложения

Коефициентът на качество, или „Q“, е важен при проверка на това колко добре работят индуктори и резонатори в електронни системи, които използват радиочестоти (RF).'Q' измерва колко добре веригата с...на 1970/01/1 63040

-

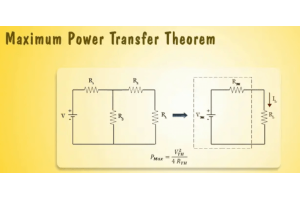

Постигане на пикова ефективност с теоремата за максимален трансфер на мощност

Теоремата за максимален пренос на мощност обяснява как енергия от източник, като батерия или генератор, преминава към свързан товар.Той показва точното състояние, при което товарът получава най -мн...на 1970/01/1 54097

-

Спецификации и съвместимост на батерията A23

Батерията A23 е малка батерия с форма на цилиндър с високо напрежение.Нарича се още 23A, 23AE или MN21, той работи на 12 волта и много по -високо от батериите на AA или AAA.Специалният му ...на 1970/01/1 52184