XC2S50-5TQG144I FPGA: Характеристики, спецификации, приложения и ръководство за програмиране

XC2S50-5TQG144I е гъвкав и мощен FPGA (полеви програмируем масив на портата) от семейството на Spartan-II на AMD Xilinx.Той е предназначен за цифрови проекти, които се нуждаят от персонализиране, скорост и надеждност.Това ръководство обяснява характеристиките, спецификациите, процеса на програмиране и използването на тази FPGA, за да ви помогне да разберете как да се възползвате максимално от него.Каталог

XC2S50-5TQG144I Преглед

The XC2S50-5TQG144I е Spartan-II FPGA от AMD Xilinx, предназначен за цифрови проекти, които се нуждаят от гъвкавост и производителност.Той има 50 000 системни порти и 1728 логически клетки, което му позволява да се справя с сложни задачи.Чипът включва 384 конфигурируеми логически блока (CLBS) и 32 768 бита на RAM, което му дава добра памет и мощност на обработка.С 92 вход/изход (I/O) пинове, той лесно може да се свърже с други компоненти.Той се предлага в 144-пинов тънък четворен пакет (TQFP), който е компактен и лесен за използване.FPGA работи на 2,5 V (с безопасен диапазон от 2.375V до 2.625V) и работи добре при температури между -40 ° C и +100 ° C.Този Spartan-II FPGA е направен с 0,18-микронна технология, което я прави ефективен и надежден.Той е програмируем, което означава, че можете да актуализирате неговите функции според нуждите.

За рентабилно, високоефективно решение, поставянето на насипно поръчка при нас е оптималният избор, осигуряващ превъзходно качество.

XC2S50-5TQG144I CAD модели

XC2S50-5TQG144I Символ

XC2S50-5TQG144I отпечатък

XC2S50-5TQG144I 3D модел

Функции XC2S50-5TQG144I

• Системни порти: XC2S50-5TQG144I FPGA предлага приблизително 50 000 системни порти.Това му позволява да поддържа сложни цифрови дизайни и приложения, изискващи значително количество възможности за обработка на логиката.

• Логически клетки: Това устройство включва 1728 логически клетки, които улесняват внедряването на сложни логически конфигурации и създаване на различни цифрови функционалности в рамките на FPGA.

• Конфигурируеми логически блокове (CLBS): Той разполага с 384 конфигурируеми логически блока (CLBS), осигурявайки основата на логиката на FPGA.Тези блокове могат да бъдат програмирани и преконфигурирани, за да отговарят на специфичните дизайнерски изисквания, подобрявайки общата гъвкавост на устройството.

• Рам: FPGA е оборудван с 32 768 бита вътрешна RAM, предлагайки ефективни възможности за съхранение и извличане на данни за задачи, включващи манипулиране на данни и временно съхранение на данни.

• I/O щифтове: С 92 I/O пина XC2S50-5TQG144I осигурява достатъчно външна свързаност, което му позволява да взаимодейства с други устройства и компоненти в система за цялостна интеграция на системата.

• Работно напрежение: Устройството работи при номинално напрежение от 2.5V, с приемлив диапазон от 2.375V до 2.625V.Този диапазон на напрежение помага да се осигури стабилна работа и надеждни характеристики при различни електрически условия.

• Температурен диапазон: XC2S50-5TQG144I е проектиран да работи ефективно в широк температурен диапазон, от -40 ° C до +100 ° C, което го прави подходящ за разполагане в среда с предизвикателни термични условия.

XC2S50-5TQG144I Блок-диаграма

Диаграмата показва как сигналите се движат навътре и извън XC2S50-5TQG144I FPGA.Той обяснява как чипът обработва входни и изходни сигнали, за да комуникира с други компоненти.На Изходна страна , сигналите идват от FPGA и преминават през единици за съхранение, наречени Flip-Flops.Тези джапанки съдържат данни и се уверете, че сигналите се променят в точното време.След това сигналите преминават през програмируем изходен буфер, който настройва колко силен е сигналът и контролира колко бързо се променя.Има и превключвател (OE контрол), който решава дали изходът трябва да бъде активен или да остане на разстояние.Защитната верига предотвратява повредата от статичното електричество, преди сигналът да достигне долни щифтове, които се свързват с други устройства.На Входната страна, сигнали отвън Въведете през програмирущия входен буфер, който ги обработва, преди да ги изпраща вътре в FPGA.Програмируемо устройство за забавяне помага да се регулира времето на сигнала, така че всичко да остане в синхрон.FPGA може също да използва вътрешно референтно напрежение (VREF), за да съответства на различни нива на напрежение, което улеснява работата с различни видове вериги.Някои I/O пинове споделят тази справка за напрежение, за да поддържат стабилни сигнали.Този дизайн помага на FPGA да управлява ефективно сигналите, като гарантира правилното време, защита и съвместимост с различни електронни компоненти.

XC2S50-5TQG144I Спецификации

|

Тип |

Параметър |

|

Производител |

AMD Xilinx |

|

Серия |

Спартан®-II |

|

Опаковане |

Табла |

|

Статус на част |

Остарял |

|

Брой лаборатории/CLB |

384 |

|

Брой логически елементи/клетки |

1728 |

|

Общи битове на RAM |

32,768 |

|

Брой на I/O. |

92 |

|

Брой порти |

50 000 |

|

Напрежение - Захранване |

2.375V ~ 2.625V |

|

Тип монтаж |

Повърхностно монтиране |

|

Работна температура |

-40 ° C ~ 100 ° C (TJ) |

|

Пакет / случай |

144-LQFP |

|

Пакет устройства за доставчици |

144-TQFP (20x20) |

|

Основен номер на продукта |

XC2S50 |

XC2S50-5TQG144I приложения

Вградени системи

В вградените системи XC2S50-5TQG144I предоставя необходимата логика за приложения, базирани на микроконтролер.Той се използва широко в автомобилната електроника, преносимите устройства и дребните роботики за подобряване на функционалността и отзивчивостта.

Обработка на сигнала

FPGA превъзхожда задачите за обработка на сигнали, където е необходима способността му да извършва паралелна обработка.Той е идеален за аудио и видео обработка, телекомуникации и анализ на данни, осигурявайки конските сили за обработка на сложни алгоритми и високоскоростни потоци от данни.

Системи за индустриален контрол

Системите за индустриален контрол се възползват от устойчивостта и програмируемостта на тази FPGA, което го прави подходящ за приложения като контрол на процесите, автоматизация на машината и мониторинг на системата.Надеждността му гарантира постоянна ефективност в среди, изискващи прецизност и оперативна стабилност.

Комуникационни системи

В комуникационните системи XC2S50-5TQG144I помага за управление на предаването и приемането на данни, поддържащи дейности като модулация на сигнала и демодулация, преобразуване на протокол и мрежово маршрутизиране.Неговата адаптивност е от ключово значение за развиващите се телекомуникационни инфраструктури и възникващите безжични технологии.

Прототипиране и развитие

FPGA също се използва широко за прототипиране на цифрови схеми.Мнозина го използват, за да тестват и усъвършенстват своите идеи преди окончателното производство, особено в сложни проекти за дизайн на ASIC и персонализиране на чипове.Тази способност намалява времето и разходите за развитие, ускорявайки пътя от концепцията към пазара.

XC2S50-5TQG144I Подобни части

XC2S50-5TQG144I Предимства

Ефективност на разходите

XC2S50-5TQG144I се откроява за своята достъпност, като доставя повече функции на долар от много конкурентни FPGA.Тази ефективност на разходите се постига чрез усъвършенствана технология на процесите и ефективна архитектура, което позволява по-широко внедряване на чувствителни към разходите пазари.

Високоефективен I/O и опаковки

Тази FPGA поддържа широк спектър от I/O стандарти и се предлага в различни рентабилни опции за опаковане.Тези функции гарантират, че устройството може да бъде интегрирано в множество приложения, без да се жертва производителността, което го прави идеален както за пазари от висок клас, така и за обем, където интерфейсната гъвкавост и физическите ограничения са фактори.

Характеристики на ниво систем

Снабден с усъвършенствани функции за управление на паметта като разпределена RAM и конфигурируема блокова RAM, XC2S50-5TQG144I подобрява ефективността на обработката на данни.Тези характеристики улесняват сложните задачи за съхранение и обработка на данни, засилване на общата производителност и мащабируемост на системата.

Препрограмируемост

Препрограмируемостта на XC2S50-5TQG144I позволява неограничени модификации към неговата конфигурация, която е полезна по време на фазата на развитие.Тази гъвкавост позволява да се усъвършенства дизайна чрез итеративни актуализации без допълнителни хардуерни разходи, насърчаване на иновациите и намаляване на времето до крайния продукт.

XC2S50-5TQG144I стъпки за програмиране

Програмирането на XC2S50-5TQG144I FPGA от серията Spartan-II на AMD Xilinx включва структурирана серия от стъпки, предназначени за ефективно превеждане на цифров дизайн във функционална FPGA конфигурация.Ето интегрирано и подробно ръководство, което да ви помогне през процеса на програмиране:

1. Запис на дизайн

Започнете с фазата на въвеждане на дизайн, където създавате вашата цифрова логика, като използвате език за описание на хардуер (HDL), като VHDL или Verilog.Тази първоначална стъпка включва подробно описание на функционалността и логиката, които искате да приложите в FPGA.Необходимо е вашият дизайн да е прецизен и точно представлява предвидените операции, за да се осигури успешен синтез и внедряване.

2. Синтез

В етапа на синтеза използвайте инструмент за синтез, за да конвертирате вашия HDL код в NetList.NetList е разбивка на вашия дизайн във формат, който включва различни взаимосвързани логически елементи като порти и джапанки.Този процес превежда вашия теоретичен дизайн в практичен план, който FPGA може да разбере и приложи.

3. Изпълнение

Изпълнението включва няколко под-стъпки: картографиране, поставяне и маршрутизиране.Картографирането присвоява елементите на вашия NetList на специфични логически блокове в FPGA.Поставянето определя физическите места на тези блокове на FPGA чипа, за да се оптимизира производителността и използването на ресурсите.Маршрутът свързва тези блокове чрез програмируемите взаимосвързани ресурси на FPGA.Тази фаза гарантира, че дизайнът отговаря на всички физически и ефективни ограничения.

4. Определение на ограничението

По време на процеса на проектиране е необходимо определяне на ограниченията.Ограниченията ръководят инструментите за внедряване, като посочвате изисквания като време (колко бързо трябва да работи FPGA) и PIN задания (които PINS на FPGA ще се свържат с различни части на вашия хардуер).Те са артикулирани във файл с ограничения на потребителите (UCF), който помага за прецизиране на дизайна за отговаряне на конкретни оперативни стандарти.

5. Битстрийм генериране

След като дизайнът ви успешно премине през фазата на внедряване, следващата стъпка е да генерирате битстрийм файл.Този файл съдържа всички данни за конфигурация, необходими на FPGA за изпълнение на дизайна.Битстриймът е крайният изход на процеса на програмиране, представляващ пълното, програмирано състояние на FPGA.

6. Програмиране на устройството

Последната стъпка е да заредите битстрийма в XC2S50-5TQG144I FPGA, което може да се направи с помощта на различни режими на конфигурация в зависимост от вашата настройка.В Главен сериен режим, FPGA автономно чете данните за конфигурация от прикачен сериен бал (програмируема памет само за четене). Сериен режим на роб Позволява външно главно устройство, като микроконтролер, да захранва серийно данните за конфигуриране на FPGA. Славещ паралелен режим Активира високоскоростно програмиране, като предоставя данни за конфигурация паралелно от външно главно устройство.И накрая, Режим на гранично сканиране (JTAG) Използва JTAG интерфейса както за програмиране, така и за тестване, което го прави полезен по време на разработката за итеративно отстраняване на грешки и проверка.

XC2S50-5TQG144I Размери на опаковката

The XC2S50-5TQG144I е полеви програмируем масив на портата (FPGA) от семейството на Spartan-II на Xilinx, настанен в a 144-пинов тънки четворни плоски пакети (TQFP).Този пакет измерва 20 mm x 20 mm.

XC2S50-5TQG144I Производител

XC2S50-5TQG144I е FPGA от семейство Spartan-II, произведено от AMD Xilinx.Xilinx, сега част от AMD, е водеща полупроводникова компания, специализирана в FPGA, адаптивни SOC и други програмируеми логически устройства.Първоначално XC2S50-5TQG144I е разработен в серията Xilinx Spartan-II, предлагайки 50 000 системни порти и 1728 логически клетки, предназначени за високоефективни, но рентабилни приложения.С придобиването на Xilinx от AMD, компанията продължава да поддържа наследени продукти като Spartan-II Series, като същевременно напредва по-новите FPGA архитектури.Въпреки това, XC2S50-5TQG144I е FPGA по-старо поколение и може да се сблъска с евентуално остаряване, тъй като AMD Xilinx се фокусира към по-напреднали FPGA семейства.

Заключение

XC2S50-5TQG144I FPGA е рентабилен и препрограмим чип, който предлага страхотна производителност и гъвкавост.Той се използва широко във вградените системи, индустриални машини и комуникационни мрежи поради високоскоростната си обработка и силни възможности за свързване.Със способността си да бъде програмирана и актуализирана, тази FPGA помага за тестване и разработване на нови идеи преди окончателното производство.Въпреки че са налични по -нови FPGA, този модел остава солиден избор за проекти, които се нуждаят от надеждно и достъпно FPGA решение.Това ръководство предоставя ясен и прост преглед на функциите, употребите и програмирането на FPGA, което го прави ценен ресурс за всички.

За нас

ALLELCO LIMITED

Прочетете още

Бързо запитване

Моля, изпратете запитване, ние ще отговорим незабавно.

често задавани въпроси [FAQ]

1. Мога ли да използвам XC2S50-5TQG144I за високоскоростни приложения?

XC2S50-5TQG144I поддържа скорост до 200 MHz, което го прави подходящ за повечето вградени и индустриални приложения.Ако обаче вашият проект изисква високоскоростни интерфейси като PCIE или DDR памет, може да се нуждаете от по-усъвършенствана FPGA като Spartan-6 или Artix-7 Series.

2. Как XC2S50-5TQG144I се сравнява с по-новия спартан-3 или спартан-6 fpgas?

Докато по-новите FPGA като Spartan-3 или Spartan-6 предлагат подобрена производителност, по-висока логическа плътност и допълнителни функции, XC2S50-5TQG144I остава предпочитан избор за чувствителни към разходите проекти с умерена сложност.Ако се нуждаете от наследствена съвместимост или стабилна верига за доставки, XC2S50-5TQG144I е чудесен вариант.

3. Какви инструменти за програмиране са съвместими с XC2S50-5TQG144I FPGA?

XC2S50-5TQG144I е програмиран с помощта на Xilinx ISE (интегрирана софтуерна среда).Докато по-новите инструменти на Xilinx като Vivado не поддържат семейство Spartan-II, ISE предоставя всички необходими функции за проектиране, синтез и програмиране за тази FPGA.

4. Мога ли да мигрирам съществуващ дизайн на Spartan-II към по-нов FPGA?

Да, но това изисква модификации.По-новите семейства Spartan-3 и Spartan-6 използват различни архитектури, нива на напрежение и методи за конфигуриране.Ако обмисляте миграцията, можем да помогнем за избора на подходящи алтернативи и минимизиране на промените в дизайна.

5. Поддържа ли XC2S50-5TQG144I програмирането на JTAG?

О: Да, FPGA поддържа JTAG (IEEE 1149.1) гранично сканиране, което позволява лесно отстраняване на грешки и конфигуриране с помощта на стандартен JTAG интерфейс.Това е полезно както за първоначалното програмиране, така и за преконфигуриране без външна памет.

XC4013XL-3PQ240C FPGA: Алтернативи, спецификации, приложения и лист с данни

на 2025/03/18

RF усилватели на мощност: Как работят, кой тип е по -ефективен

на 2025/03/18

Популярни публикации

-

Компютри на сложни инструкции: Как промениха изчисленията?

на 8000/04/18 147766

-

USB-C Pinout и функции

на 2000/04/18 111994

-

Използване на Xilinx Unified Simulation Primitives: Изчерпателно ръководство за FPGA дизайн и симулация

на 1600/04/18 111351

-

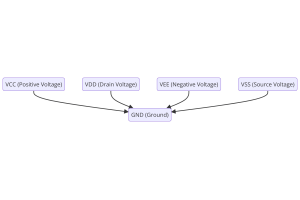

Захранващи напрежения в електрониката: Значение на VCC, VDD, VEE, VSS и GND

на 0400/04/18 83756

-

Ръководство за конектор RJ45: Pinout, окабеляване, видове кабели и употреби

на 1970/01/1 79550

-

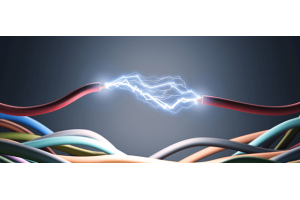

Крайното ръководство за цветни кодове в съвременните електрически системи

Начинът, по който нашите електрически системи използват цветове, не е само за външен вид.Всеки цвят на проводника сега показва специфична функция, което улеснява идентифицирането и обработката на е...на 1970/01/1 66951

-

Ръководство за клапа на чист: функция, симптоми, тестване и подмяна на оптимална работа на двигателя

Клапанът на чистката е ключова част от системата на автомобила, която помага да се поддържа чистият въздух, като управлява изпаренията на горивото, преди да могат да избягат в атмосферата.Това не с...на 1970/01/1 63094

-

Качество (Q) Фактор: Уравнения и приложения

Коефициентът на качество, или „Q“, е важен при проверка на това колко добре работят индуктори и резонатори в електронни системи, които използват радиочестоти (RF).'Q' измерва колко добре веригата с...на 1970/01/1 63028

-

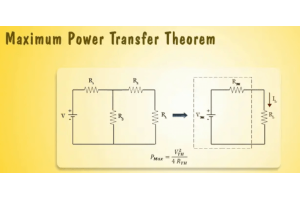

Постигане на пикова ефективност с теоремата за максимален трансфер на мощност

Теоремата за максимален пренос на мощност обяснява как енергия от източник, като батерия или генератор, преминава към свързан товар.Той показва точното състояние, при което товарът получава най -мн...на 1970/01/1 54094

-

Спецификации и съвместимост на батерията A23

Батерията A23 е малка батерия с форма на цилиндър с високо напрежение.Нарича се още 23A, 23AE или MN21, той работи на 12 волта и много по -високо от батериите на AA или AAA.Специалният му ...на 1970/01/1 52176