XC4VLX100-10FFG1148C FPGA: функции, спецификации, приложения и ръководство за програмиране

Ако работите със сложни цифрови дизайни, XC4VLX100-10FFG1148C ви дава необходимата мощност и гъвкавост.Този FPGA опакова висок логически капацитет, вградена памет и голям брой I/O пинове, което го прави идеален за взискателни приложения.В това ръководство ще научите за неговите функции, производителност, параметри на времето, приложения, стъпки за програмиране, плюсове и минуси, детайли за опаковане и производител.Каталог

Какво представлява XC4VLX100-10FFG1148C?

The XC4VLX100-10FFG1148C е високоефективен FPGA от Xilinx (сега AMD), принадлежащ към семейството на Virtex-4 LX, което е построено на меден процес 90 nm.Това устройство е предназначено за сложни цифрови логически реализации и е част от серията LX, която подчертава логическите и паметните ресурси без високоскоростни серийни приемо-предаватели.Идентифициран от своя FCBGA пакет от 1148 Ball и търговска температура, той представлява една от опциите с по-голям капацитет в състава на LX.

Търсите xc4vlx100-10ffg1148c?Свържете се с нас, за да проверите текущите запаси, времето за изпълнение и ценообразуването.

XC4VLX100-10FFG1148C функции

• Висок логически капацитет

XC4VLX100-10FFG1148C осигурява 110 592 логически клетки, което позволява внедряването на сложни цифрови дизайни на едно устройство.Този голям логически капацитет го прави подходящ за функции за обработка и контрол с висока плътност.

• Вградена и разпределена памет

Той интегрира около 4,22 MBITs обща памет, комбинирайки блокова RAM и разпределена RAM.Тази архитектура на паметта поддържа ефективно съхранение на данни, буфериране и обработка на чип, без да е необходимо обширна външна памет.

• Обширни входно/изходно ресурси

Устройството предлага 768 потребителски I/O пинове, което дава гъвкавост за взаимодействие с различни външни компоненти и системи.Тези I/OS поддържат широк спектър от стандарти чрез функцията Selectio ™, подобряване на свързаността на нивото на дъската.

• Високопроизводително ядро

Работейки при 1,2 V основно напрежение, FPGA поддържа вътрешно часовник до приблизително 500 MHz, осигурявайки бърза логическа производителност.Това гарантира надеждна работа при взискателни високоскоростни приложения.

• Търговски температурен диапазон

Оценено за 0 ° C до +85 ° C, устройството е проектирано за среди от търговски клас.Той поддържа стабилна ефективност при типични работни условия за индустриални и вградени системи.

Референтни параметри на времето за часовник

Диаграмата показва измерванията на времето за повишаване и падане на часовника за XC4VLX100-10FFG1148C, като се фокусира върху tRclk (Време за издигане) и tFclk (Време за падане) между 20% и 80% нива на напрежение на сигнала на часовника.Той илюстрира колко бързо преходите на часовника от ниско към високо и високо към ниско, което е чудесно за поддържане на целостта на времето и надеждна работа на FPGA.Прецизният контрол на тези ръбове осигурява точна синхронизация на вътрешната логика и външните интерфейси.В XC4VLX100-10FFG1148C поддържането на правилното повишаване и падане е важно за стабилни високоскоростни характеристики и минимизиране на изкривяването на сигнала.

Обобщена настройка на теста

Диаграмата илюстрира генерализираната настройка на теста, използвана за измерване на закъсненията на изхода и характеристиките на сигнала на XC4VLX100-10FFG1148C FPGA.Референтен резистор (RRef) и кондензатор (cRef) са свързани към изхода FPGA, с vИзмерване Представяне на нивото на напрежение, при което се правят измервания на времето.Тази стандартизирана настройка гарантира последователно и точно измерване на закъсненията на прехода на сигнала в различни тестови среди.За XC4VLX100-10FFG1148C това е важно за валидиране на високоскоростни I/O производителност и гарантиране, че устройството отговаря на спецификациите на времето в реални приложения.

XC4VLX100-10FFG1148C Спецификации

|

Тип |

Параметър |

|

Производител |

AMD/Xilinx |

|

Серия |

Virtex®-4 LX |

|

Опаковане |

Табла |

|

Статус на част |

Активен |

|

Брой лаборатории/CLB |

12288 |

|

Брой логически елементи/клетки |

110592 |

|

Общи битове на RAM |

4423680 |

|

Брой на I/O. |

768 |

|

Напрежение - захранване |

1.14 V ~ 1.26 V |

|

Тип монтаж |

Повърхностно монтиране |

|

Работна температура |

0 ° C ~ 85 ° C (TJ) |

|

Пакет / случай |

1148-BBGA, FCBGA |

|

Пакет устройства за доставчици |

1148-FCPBGA (35 × 35) |

|

Основен номер на продукта |

Xc4vlx100 |

XC4VLX100-10FFG1148C приложения

1. Системи за обработка на цифрови сигнали (DSP)

XC4VLX100-10FFG1148C е добре подходящ за внедряване на високоефективни DSP алгоритми благодарение на големия си логически капацитет и вградената памет.Можете да изградите по поръчка тръбопроводи за обработка, които обработват интензивни изчисления навреме.Това го прави идеален за приложения като обработка на изображения, радарни системи и разширено филтриране.

2. Вградено ускорение на системата

Със своята гъвкава архитектура устройството се използва широко за ускоряване на вградените системни функции като обработка на протокол, управление на шината и хардуерно разтоварване.Чрез прехвърляне на задачи от софтуер към FPGA плат, това подобрява отзивчивостта на системата.Това дава възможност за оптимизиране на производителността, като същевременно поддържа гъвкавостта на дизайна.

3. Оборудване за комуникации и мрежи

Възможностите за големи входно/изброени и обработващи възможности на FPGA го правят подходящ за комуникационна инфраструктура, включително превключватели, рутери и мостове на интерфейс.Той може да управлява сложни мрежови протоколи и потоци от данни с висока лента с ниска латентност.Това го прави надежден избор за мрежи и системи за центрове за данни на гръбнака.

4. Високоскоростно събиране и обработка на данни

XC4VLX100-10FFG1148C се отличава в приложения, които изискват бързо заснемане и обработка на данни, като инструменти и научно оборудване.Вградената му памет и логически ресурси позволяват бързо буфериране и паралелно манипулиране на данни.Това гарантира ефективно обработка на големи обеми на данни в среда.

XC4VLX100-10FFG1148C Подобни части

|

Спецификация |

XC4VLX100-10FFG1148C |

XC4VLX100-10FFG1148I |

XC4VLX100-11FFG1148C |

XC4VLX100-10FF1148C |

XC4VLX100-10FFG1513C |

XC4VLX100-12FFG1148C |

|

Производител |

Xilinx (AMD) |

Xilinx (AMD) |

Xilinx (AMD) |

Xilinx (AMD) |

Xilinx (AMD) |

Xilinx (AMD) |

|

Семейство |

Virtex-4 LX |

Virtex-4 LX |

Virtex-4 LX |

Virtex-4 LX |

Virtex-4 LX |

Virtex-4 LX |

|

Логическа способност |

110 592 клетки |

110 592 клетки |

110 592 клетки |

110 592 клетки |

110 592 клетки |

110 592 клетки |

|

Тип пакет |

FCBGA |

FCBGA |

FCBGA |

FCBGA |

FCBGA |

FCBGA |

|

Брой на топката |

1148 |

1148 |

1148 |

1148 |

1513 |

1148 |

|

Степен на скорост |

–10 |

–10 |

–11 |

–10 |

–10 |

–12 |

|

Температурна степен |

Търговски (в) |

Индустриални (i) |

Търговски (в) |

Търговски (в) |

Търговски (в) |

Търговски (в) |

|

Основно напрежение |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

|

Работен температурен диапазон |

0 ° C до +85 ° C |

–40 ° C до +100 ° C |

0 ° C до +85 ° C |

0 ° C до +85 ° C |

0 ° C до +85 ° C |

0 ° C до +85 ° C |

|

Разлика |

Базова част, стандартна PKG |

Поддръжка на индустриалната температура |

По -висока скорост |

Липсва обозначение „G“ |

По -голям пакет, повече I/O |

Най -бързата степен на скорост в серии |

XC4VLX100-10FFG1148C стъпки за програмиране

Преди да програмирате XC4VLX100-10FFG1148C, трябва да гарантирате, че вашата среда за разработка и конфигурационни файлове са правилно настроени.Устройството поддържа множество режими на конфигурация, така че избирането на правилния ранен осигурява гладък и успешен процес на програмиране.

1. Захранвайте устройството

Започнете с прилагане на мощност към FPGA, като използвате необходимите релси на напрежението (VCCINT, VCCAUX и VCC_CONFIG).Трябва да се уверите, че тези напрежения достигат стабилни нива, преди да започне някаква конфигурация.Правилното последователност на мощността е добре, за да се избегнат грешки в инициализацията.

2. Изберете режим на конфигурация

На следващо място, FPGA пробива своите режими на режима на нарастващия ръб на init_b, за да определи кой метод на конфигурация да се използва.Можете да избирате от JTAG, робски сериен, главен сериен или SelectMap, в зависимост от вашата настройка.Уверете се, че щифтовете на режима са зададени правилно, тъй като те контролират как ще бъде зареден битстрийм.

3. Инициализирайте устройството

FPGA изчиства конфигурационната си памет и се подготвя за зареждане на битстрийм по време на инициализация.На този етап сигнали като init_b, gwe и gts се използват за поставяне на устройството в известно състояние.Трябва да се уверите, че всички сигнали за инициализация се държат според очакванията, преди да продължат.

4. Заредете битайма

Използвайки избрания от вас интерфейс, сега предавате конфигурационния бит поток в FPGA.Например, ако използвате JTAG, битстъм се измества серийно в конфигурационната памет на устройството.За успешното програмиране е необходим точен и пълен трансфер на битстрийм.

5. Стартирайте процеса на конфигурация

След като битстъмът е напълно зареден, FPGA излиза от режим на смяна и започва последователността на стартиране.Команда JSTART или еквивалентен процес задейства устройството за финализиране на конфигурацията.Трябва да позволите на FPGA да завърши този етап без прекъсвания.

6. Попълнете конфигурацията и въведете потребителски режим

FPGA автоматично проверява целостта на битстрийм, използвайки CRC и, ако е валидна, отстоява зададения сигнал.След като това се случи, логиката на потребителя става активна и устройството работи според вашия дизайн.В този момент процесът на конфигурация е завършен и FPGA е напълно функционален.

7. Незадължителна проверка

И накрая, можете да извършите стъпка за четене или проверка, за да гарантирате, че конфигурацията е била успешна.Това може да стане чрез JTAG или SelectMap, в зависимост от използвания от вас режим.Въпреки че е незадължително, силно се препоръчва системите да потвърждават правилното програмиране.

XC4VLX100-10FFG1148C Предимства и недостатъци

Предимства

• По -ниска обща консумация на енергия в сравнение с много 90 nm FPGA.

• Подкрепена от зряла и стабилна дизайнерска екосистема.

• Силно съотношение между производителност и цена за своето поколение.

• Модулната архитектура на ASMBL подобрява ефективността на дизайна.

• Надеждна, доказана платформа за отдавна установени дизайни.

Недостатъци

• Въз основа на наследената технология с ограничена бъдеща подкрепа.

• Липсва високоскоростни серийни приемо-предаватели, открити в по-новите семейства.

• По -ниска мащабируемост и гъвкавост в сравнение със съвременните FPGA.

• Потенциални предизвикателства за снабдяване поради възрастта на продукта.

• Изисква внимателна мощност и термично управление при високо използване.

Xc4vlx100-10ffg1148c Размери на опаковки

|

Параметър |

Размери |

|

Тип пакет |

FFG1148 (Flip-Chip Fine-Pitch BGA) |

|

Топка стъпка |

1,00 mm |

|

Размер на тялото на пакета (L × W) |

35,00 mm × 35,00 mm |

|

Размер на тялото на пакета (L × W, инч) |

1.378 в × 1.378 в |

|

Обща височина на пакета (a) |

3,40 мм (типично) |

|

Обща височина на пакета (A, инч) |

0,134 инча (типично) |

|

Толерантност на размера на тялото |

± 0.20 mm |

|

Топка масив |

34 × 34 (1,00 мм решетка за стъпка) |

|

Брой на топката |

1,148 топки |

|

Диаметър на топката (номинален) |

0,60 mm |

|

Дебелина на субстрата (B) |

~ 1,00 mm |

|

Височина на противопоставяне (A1) |

0,40 mm (номинална) |

|

Размер на топлината / метална капачка размер |

~ 32 мм квадрат (типична площ от топ метал) |

|

Тип монтаж |

Повърхностно монтиране |

XC4VLX100-10FFG1148C Производител

XC4VLX100-10FFG1148C се произвежда от Xilinx, пионер в областта на програмируемите логически устройства.През 2022 г. Xilinx става част от AMD (Разширени микро устройства), допълнително засилване на позицията му във високоефективни изчислителни и адаптивни технологии.Това сливане съчетава експертния опит на FPGA на Xilinx с лидерството на AMD за обработка, като гарантира стабилна дългосрочна поддръжка и иновации за продукти като XC4VLX100-10FFG1148C.

Заключение

XC4VLX100-10FFG1148C се откроява с големия си брой на логическите клетки, гъвкавата архитектура на паметта, широки възможности за входно/изходно ниво и солидна ефективност в рамките на своето поколение.Той поддържа високоскоростна цялост на сигнала и надеждна цялост, което го прави подходящ за взискателни приложения в DSP, мрежи и вградени системи.Въпреки че предлага доказана стабилност и зряла екосистема, тя отразява наследената технология с известни ограничения за мащабируемост и снабдяване, което прави внимателното внимание за съвременните дизайни.

DataSheet PDF

Xc4vlx100-10ffg1148c таблици с данни:

За нас

ALLELCO LIMITED

Прочетете още

Бързо запитване

Моля, изпратете запитване, ние ще отговорим незабавно.

често задавани въпроси [FAQ]

1. Как XC4VLX100-10FFG1148C се сравнява с по-новите FPGA семейства?

По-новите семейства като Virtex-6, 7-Series или Ultrascale предлагат по-високи скорости, по-ниска мощност и интегрирани серийни приемо-предаватели.Въпреки това, XC4VLX100-10FFG1148C осигурява отлична стойност за стабилни наследени системи, които не изискват най-новите функции.

2. Какви инструменти за разработка са съвместими с XC4VLX100-10FFG1148C?

Можете да използвате Xilinx ISE Design Suite за синтез, внедряване и генериране на битстрийм.Тъй като това е по -старо FPGA семейство, по -новите инструменти като Vivado не го поддържат, така че не забравяйте да имате съвместима среда за развитие.

3. Можете ли да използвате XC4VLX100-10FFG1148C в температурни среди?

Това устройство е оценено за търговски температурен диапазон от 0 ° C до +85 ° C, което го прави подходящ за повечето стандартни индустриални и вградени условия.За по -сурови среди може да се изисква версия с удължен температурен диапазон.

4. Може ли XC4VLX100-10FFG1148C да се използва за високоскоростни приложения за обработка на данни?

Да.С вътрешен часовник 500 MHz и голям логически капацитет, той обработва ефективно обработката на сигнали с висока скорост.Въпреки това, ще трябва да проектирате правилни ограничения за времето и оформления на ниво дъска, за да увеличите максимално производителността.

5. Изисква ли XC4VLX100-10FFG1148C специално охлаждане или термично управление?

При високо използване тази FPGA може да генерира значителна топлина.Трябва да осигурите подходящ въздушен поток, радика или термичен дизайн на ниво дъска, за да поддържате производителността и да избягвате дросела или дългосрочни щети.

BCM5221KPB Ethernet PHY: Характеристики, блок -схема, приложения и лист с данни

на 2025/10/12

Как да избирате предпазители за бързо изтръпване и бавен удар, за да защитите захранващите вериги

на 2025/10/11

Популярни публикации

-

Компютри на сложни инструкции: Как промениха изчисленията?

на 8000/04/18 147778

-

USB-C Pinout и функции

на 2000/04/18 112027

-

Използване на Xilinx Unified Simulation Primitives: Изчерпателно ръководство за FPGA дизайн и симулация

на 1600/04/18 111351

-

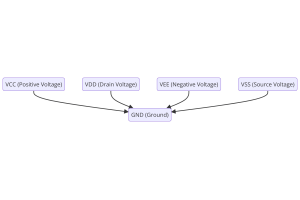

Захранващи напрежения в електрониката: Значение на VCC, VDD, VEE, VSS и GND

на 0400/04/18 83780

-

Ръководство за конектор RJ45: Pinout, окабеляване, видове кабели и употреби

на 1970/01/1 79578

-

Крайното ръководство за цветни кодове в съвременните електрически системи

Начинът, по който нашите електрически системи използват цветове, не е само за външен вид.Всеки цвят на проводника сега показва специфична функция, което улеснява идентифицирането и обработката на е...на 1970/01/1 66969

-

Ръководство за клапа на чист: функция, симптоми, тестване и подмяна на оптимална работа на двигателя

Клапанът на чистката е ключова част от системата на автомобила, която помага да се поддържа чистият въздух, като управлява изпаренията на горивото, преди да могат да избягат в атмосферата.Това не с...на 1970/01/1 63107

-

Качество (Q) Фактор: Уравнения и приложения

Коефициентът на качество, или „Q“, е важен при проверка на това колко добре работят индуктори и резонатори в електронни системи, които използват радиочестоти (RF).'Q' измерва колко добре веригата с...на 1970/01/1 63041

-

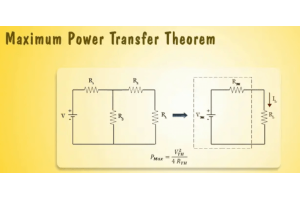

Постигане на пикова ефективност с теоремата за максимален трансфер на мощност

Теоремата за максимален пренос на мощност обяснява как енергия от източник, като батерия или генератор, преминава към свързан товар.Той показва точното състояние, при което товарът получава най -мн...на 1970/01/1 54097

-

Спецификации и съвместимост на батерията A23

Батерията A23 е малка батерия с форма на цилиндър с високо напрежение.Нарича се още 23A, 23AE или MN21, той работи на 12 волта и много по -високо от батериите на AA или AAA.Специалният му ...на 1970/01/1 52191