Овладяване на SR резюмета: символи, функции и практически приложения

SR -ключалката е асинхронна схема, която работи независимо от сигналите на часовника, което го прави универсален инструмент в различни приложения.Той поддържа двоично състояние - или високо (1) или ниско (0) - и може да съхранява един бит информация, която държи, докато новите входни сигнали не диктуват промяна.Този основен двоичен елемент за съхранение е конструиран с помощта на две кръстосани логически порти, обикновено нито порти на NAND.Зададеният вход (и) активира ключалката, като настройва изхода (q) на висок, докато входът за нулиране (R) задава изхода на ниско.Въпреки това, едновременните високи сигнали на двата входа водят до неопределено състояние, дизайнерите на условия трябва да избягват.SR ключалките не са само теоретични конструкции;Те се реализират в практически системи за съхраняване на временни данни, поддържане на междинни резултати от обработка и дори управляват откриване на грешки в критични приложения като аерокосмически и медицински изделия, като показват своята незаменим в дизайна на цифровите вериги.Каталог

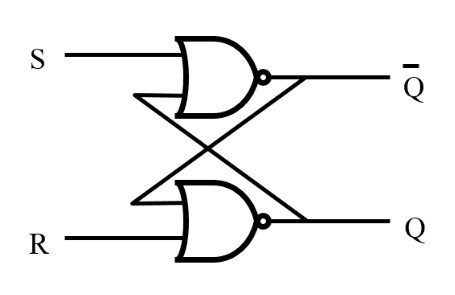

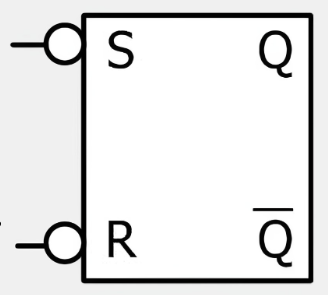

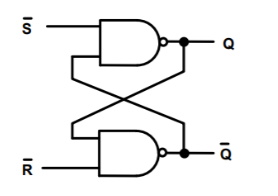

Фигура 1: SR Latch

Какво е SR ключалка?

SR резюме или резюме на Set-Reset е основен двоичен елемент за съхранение, който принадлежи към категорията асинхронни схеми.За разлика от синхронните вериги, SR ключалките работят без часовник сигнал, разчитайки единствено на директното управление на входните сигнали.Това им позволява да функционират независимо в цифровите схеми.SR ключалката може да поддържа две стабилни състояния: високо (1) и ниско (0), което му позволява да съхранява един бит информация, докато не се актуализира от нови входни сигнали.

Конструирането на SR ключалка обикновено включва две кръстосани логически порти, обикновено нито порти или порти на NAND.В дизайна на SR Latch с помощта на нито порти изходът на всяка порта е свързан към входа на другия, образувайки цикъл за обратна връзка.Тази конфигурация гарантира, че ключалката може бързо да промени състоянията въз основа на входните сигнали, като същевременно поддържа стабилност, докато нов вход не предизвика промяна.

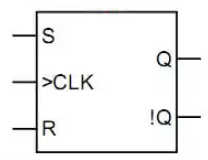

Фигура 2: SR ключалка (2)

Задайте вход (и): Когато зададеният вход (и) е активиран (висок), изходът на ключалката (q) преминава на висок (1).

Нулиране на входа (R): Когато входът за нулиране (R) е активиран (висок), изходът (q) превключва на ниско (0).

И двата входа са високи: Ако и входовете S и R са високи едновременно, резето влиза в неопределено състояние, което трябва да се избягва в дизайна.

SR ключалките са от съществено значение за временното съхранение на данни и междинните резултати в цифровите системи.Те са основополагащите елементи в по-сложни последователни схеми като многобитни регистри за смяна, единици за памет и някои видове броячи.

В тези приложения SR ключалките осигуряват стабилно задържане на данни и могат бързо да реагират на промени във външните сигнали, като гарантират ефективната работа на цялата електронна система.

Друго критично приложение на SR ключалките е в логиката на откриване на грешки и логиката на корекция в цифровите схеми.Поради способността си да държат стабилно състояние, те могат да наблюдават промените в състоянието на системата и бързо да се върнат към предварително определено безопасно състояние при откриване на аномалия.Тази функция е особено ценна в системите с висока надеждност като аерокосмически и медицински изделия.

Символ на SR ключалката

Разбирането на неговия символ и структура е от основно значение за схващане на неговата работа и практическа употреба.В диаграмите на веригата, SR ключалката обикновено има два основни входни порта, обозначени S (SET) и R (RESET).Тези входове контролират изходното състояние на Latch, обикновено представено като Q. Някои дизайни също се отличават с обратния изход, обозначен Q ', който осигурява обратното състояние на Q.

Фигура 3: Символ на ключалката на SR

SR ключалката често е представена от правоъгълен символ с входове S и R и изход Q. В някои случаи е показан и изходът Q '.Това ясно етикетиране позволява на дизайнерите на вериги бързо да идентифицират функцията на компонента и неговата роля в по -голямата верига.

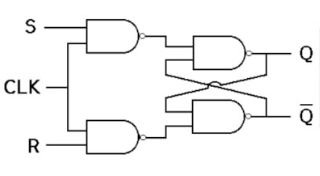

Общият вариант на SR ключалката включва вход за часовник (CLK).Входът на CLK гарантира, че промените в състоянието настъпват в синхрон със сигнала на часовника, което позволява прецизно управление на времето.В тази настройка, дори ако S или R е активиран, състоянието на ключалката се актуализира само когато CLK сигналът отговаря на специфични условия, обикновено на ръба на издигането или падането.Това предотвратява грешките, причинени от входните сигнални проблеми или непредвидени промени.

Фигура 4: Символ на затвора с часовник SR ключалка

Символът на часовника SR Latch включва входовете S, R и CLK вътре в правоъгълник.Това стандартизирано представяне помага на дизайнерите да разберат функционалността на ключалката и нейните изисквания за време.Например, при високоефективни изчислителни или сложни системи за пренос на данни внимателното CLK контролираше, че данните се съхраняват и прехвърлят точно на всеки етап на обработка, като оптимизират цялостната ефективност и надеждността на системата.

Прецизният контрол на входовете на SR Latch е важен, особено при проектирането на високоскоростна и памет с голям капацитет или временни буфери за данни.Чрез проектиране на логически схеми за управление на S и R активиране могат да се постигнат сложни функции като зареждане на данни, изчистване или състояние на състояние.Точният контрол на CLK сигнала гарантира, че всички операции с данни следват предварително определена последователност на времето, като значително повишават ефективността на системата и способността за обработка на данни.

Дълбокото разбиране на символа и структурата на SR Latch подпомага не само в правилния дизайн и отстраняване на проблеми, но и при изпълнение на сложни цифрови логически операции и подобряване на производителността на системата.Това е особено критично в приложения, изискващи висока надеждност и прецизен контрол, като аерокосмически и медицински изделия.

Видове ключалки и техните работни принципи

Ключовете са основни компоненти в електронния дизайн, предлагащи различни функции и широки приложения.Основните видове ключалки са SR ключалки и D ключалки, всеки с уникални операции и случаи на използване.

SR ключалка

SR Latch или Set-Reset Latch е основно устройство за съхранение, контролирано от двата му входа, S (SET) и R (RESET).

Когато входът S получава висок сигнал, изходът Q става висок, което показва, че данните са зададени.Когато R входът получи висок сигнал, изходът Q става нисък, което показва, че данните са нулирани.Ако и двете S и R входа са високи едновременно, резето влиза в неопределено състояние, което води до потенциална нестабилност на изхода.Това състояние трябва да се избягва в дизайна.Директният отговор на SR Latch към входните сигнали го прави полезен в ситуации, изискващи бърза реакция.

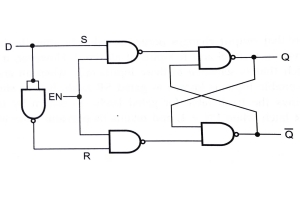

D LATCH

Записването на D, известна още като ключалка на данни или прозрачен капак, предлага по -сложен контрол с CLK в въвеждане на данни D и Clock Signal.

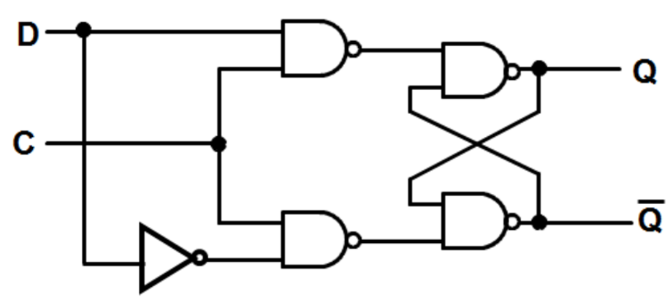

Фигура 5: D Запазване

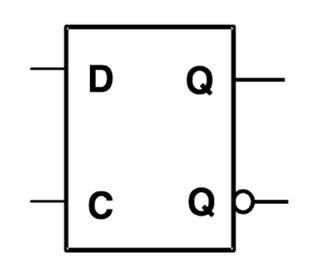

Фигура 6: D Символ на закрепването

Когато CLK е висок, изходът Q следва входа d, което позволява данните да преминават свободно през ключалката.Когато CLK намалява, токът на D е заключен, а изходът Q остава постоянен до следващия CLK висок сигнал.Този механизъм прави D Latch идеален за временно съхраняване на данни за синхронизиране на различни скорости на обработка в рамките на дадена система.

SR и D Latches имат несравнима роля в съхранението на данни и логиката на състоянието на машината.Поради реакцията на директното им ниво на входно ниво, ключалките са от съществено значение за проектирането на асинхронни вериги.Те предоставят жизненоважни функции за сложни трансфери на данни и системи за управление на захранването, като ефективно съхраняват информация за състоянието, за да се осигури стабилна работа.Правилното използване на тези ключалки може значително да подобри надеждността и ефективността на веригата, което ги прави незаменими в съвременните електронни системи.

Истинска таблица на SR резюме

Фигура 7: Latch на SR NAND

|

S |

R |

Q |

Q ' |

Забележка |

|

0 |

0 |

1 |

1 |

Забранено |

|

0 |

1 |

1 |

0 |

Комплект |

|

1 |

0 |

0 |

1 |

Нулиране |

|

1 |

1 |

Q |

Q ' |

Задържайте |

Диаграма 1: Таблица за истината на SR Latch с помощта на NAND Gates

Фигура 8: SR, нито ключалка

|

S |

R |

Q |

Q ' |

Забележка |

|

0 |

0 |

Q |

Q ' |

Задържайте |

|

0 |

1 |

1 |

0 |

Нулиране |

|

1 |

0 |

0 |

1 |

Комплект |

|

1 |

1 |

0 |

0 |

Забранено |

Диаграма 2: Таблица за истината на SR Latch с помощта на нито порти

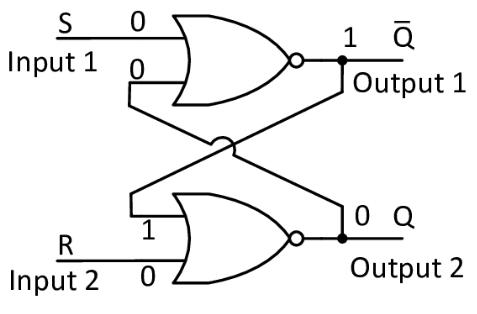

Сега приемаме таблицата за истината на SR ключалката, използвайки Nor Gate като пример, за да разберем значението на таблицата на истината на SR Latch.

Входни и изходни състояния

И S, и R са 0: Резето остава в сегашното си състояние.Изходът q остава същият, независимо дали е 0 или 1.

S е 0, а R е 1: Резервата се нулира, принуждавайки изхода q до 0.

S е 1, а R е 0: Комплектите, което прави изхода q равен на 1.

И S, и R са 1: Това условие е невалидно или неопределено, често наричано състояние "забранено" в SR ключалка.В този случай q и q 'и двете равни 0, което води до двусмислен изход.

Когато S и R са и 0, ключалката не прави нищо и просто държи текущата си стойност.Това е полезно за поддържане на състоянието без промени.

Когато S е 0 и R е 1, на резето е изрично казано да се нулира, като се уверите, че Q е 0, независимо от предишното му състояние.Това е пряк начин за изчистване на ключалката.

Когато S е 1 и R е 0, резето е зададено, като се гарантира, че Q става 1. Ето как съхранявате „1“ в резето.

Когато S и R са и 1, състоянието не е разрешено, защото причинява и двата изхода да са 0, което е противоречиво и ненадеждно.Дизайнерите трябва да избягват това състояние, за да осигурят стабилна работа.

Предимства и недостатъци на ключалките

Ключовете се използват широко в дизайна на цифровите вериги поради тяхната простота и ниска цена.Тези характеристики позволяват на ключалките да работят с висока скорост с ниска консумация на енергия, което ги прави идеални за високоскоростни цифрови системи.Например, в файлове за регистриране на процесори, Latches могат бързо да съхраняват и извличат данни, като значително повишават скоростта и ефективността на обработката.

Предимства на ключалките

Простота и ефективност на разходите: Редките са ясни компоненти, които са евтини за изпълнение в цифровите схеми.

Висока скорост и ниска мощност: Техният дизайн позволява бърза работа с минимална консумация на енергия, което е от решаващо значение за високоскоростните цифрови системи.

Ефективност в обработката на данни: В приложения като файлове на регистъра на процесора Latches осигуряват бързо съхранение и извличане на данни, подобряване на цялостната производителност на системата.

Недостатъци на ключалките

Въпреки своите предимства, ключалките имат забележителни ограничения в определени дизайни и приложения.

Непредсказуемо поведение при асинхронни дизайни: Без контрол на сигнала на часовника, ключалките могат да се държат непредсказуемо.В SR ключалките, ако и входовете на Set (S), и Reset (R) са високи едновременно, изходът става неопределен, което води до нестабилност.Това е проблематично при контролни или критични за безопасността приложения, където надеждният изход е от решаващо значение.

Сложният дизайн на времето: Проектирането с ключалки изисква внимателни съображения за времето.Инженерите трябва да отчитат забавянето на разпространението на сигнала и условията на състезанието, за да избегнат грешките на времето.Неправилното дизайн може да доведе до промени в данните, преди да се стабилизира часовникът, причинявайки корупция на данните или неправилно улавяне на данни.Това налага дълбоко разбиране на анализа на времето и поведението на веригата.

За да се справят с тези предизвикателства, могат да се използват специфични техники и стратегии за проектиране:

Механизми за синхронизация: Добавянето на механизми за синхронизация може да помогне за управление на асинхронни входове и смекчаване на непредсказуемото поведение.

Персонализирано управление на часовника: Прилагането на персонализирани стратегии за управление на часовника може да гарантира, че данните са съответствани правилно и в правилните моменти.

Използване на инструменти на EDA: Съвременните инструменти за автоматизация на електронния дизайн (EDA) предлагат разширени възможности за анализ и оптимизация.Тези инструменти помагат да се прогнозират и разрешат проблемите на времето и синхронизацията по време на фазата на проектиране, като подобряват надеждността и производителността на цифровите системи с помощта на ключалки.Те помагат на дизайнерите да идентифицират потенциални проблеми рано, като гарантират, че крайният продукт работи надеждно при различни условия.

Практически приложения на SR резюмета

SR -ключалките, известни със способността си за бързо и надеждно поддържане на състоянието, се използват широко в различни електронни системи.Те се отличават в сценарии, изискващи временно съхранение на данни или задържане на държавата.

Временно съхранение на данни

SR ключалките често се използват в кеш паметта за временно съхраняване на данни.Това позволява на системата бързо да има достъп до често използвани данни, като значително повишава възможностите за обработка на данни и ефективността на мащабните процесори.

Файлове за регистър на съхранението

В процесорите SR Latches дават възможност за бързо съхранение и извличане на данни в регистрирани файлове, подобряване на скоростта на обработка и цялостната производителност на системата.

Поддържане на контролни сигнали

В системите за цифрово управление, SR ключалките са полезни за поддържане на състоянието на определени контролни сигнали, докато външните условия или логиката на системата не диктуват промяна.Също така, те помагат за задържане на състояния в системата, като гарантират постоянна работа в операциите, които изискват прецизност и надеждност.

Спусъци и насрещни вериги

SR-фиксираните джапанки се използват често в вериги, изискващи синхронизирана работа, като цифрови часовници и таймери.Те контролират броя на импулсите, като гарантират точното време и надеждното представяне.Тези схеми разчитат на SR ключалки за поддържане на точни бройки, което улеснява времето и секвенирането в цифровите системи.

Механични взаимодействия

SR ключалките са ефективни за елиминиране на механичния отскок в превключвателите.Механичен отскок възниква, когато превключвателят генерира бързи, повтарящи се сигнали се променят поради лош контакт.SR Latches стабилизират изходния сигнал, предотвратявайки грешки, причинени от шумни сигнали.

SR Flip-Flop

SR Flip-Flop, често наричан ръб, задействан от сет-разстояния Flip-Flop, се състои от две взаимосвързани SR ключалки.Тази структура на двойно приковаване му позволява да реагира на специфични ръбове на сигнала на часовника (или нарастващо или падане), за да промени състоянието си.Това се постига чрез специален логически контрол между ключалките.Изходът на първото заключване става част от входа за втория резюме, а изходът на втория резюме от своя страна влияе върху първото заключване, създавайки заключващ цикъл за обратна връзка.

Фигура 7: SR Flip-Flop

SR Flip-Flop се променя точно на повишаването или падащия ръб на сигнала на часовника.Заключителната обратна връзка между двете SR реколта гарантира, че флип-флоп се променя само състоянието в отговор на ръба на часовника, осигурявайки стабилен и надежден изход.

В микропроцесорите и процесорите на цифрови сигнали се използват SR джапанки за вземане на проби и съхранение на данни.Те улавят и стабилизират данни в определени ръбове на часовника, като гарантират надеждна последваща обработка и анализ на данни.

Механизмът за задействане на ръба помага да се избегнат условията на състезанието, при които различните части на веригата могат да променят състоянието едновременно без синхронизация, което потенциално води до нестабилни или неправилни изходи.SR Flip-Flops са от решаващо значение за прилагането на специфична логика на комуникационния протокол, като синхронизация на рамката и откриване на грешки.Тяхната стабилност и бързото време за реакция помагат да се поддържа качеството на предаване на данни и надеждността на системата.

Забранени състояния в SR реколта и SR джапанки-флопи

Когато проектираме SR резюмета и SR джапанки, използвайки NAND и NOR порти, всички ние трябва да обърнем внимание на управлението и избягването на инхибирани състояния.Забранено състояние възниква, когато входовете на множеството (ите) и нулиране (R) са едновременно високи (за NAND порти) или ниски (за NOR порти).Тази комбинация води до неопределено изходно състояние, тъй като изходът зависи от предишното състояние на веригата, което го прави непредсказуем.

Забранени държави в NAND GATE SR LATCES

Когато и S, и R са ниски, и двата изхода отиват високо, което нарушава характеристиката на допълващата продукция на ключалката.Това води до неопределено състояние.

Забранени състояния в NOR Gate SR Latches

Когато и S, и R са високи, и двата изхода намаляват, също така създават неопределено състояние.Това може да доведе до непредсказуемо поведение във веригата.

Практически подходи, за да се избегнат забранени държави

Добавяне на контролна логика

Използвайте допълнителни логически порти, за да наблюдавате състоянията на S и R. Ако и двата входа тенденция към забранено състояние, автоматично коригирайте един вход, за да предотвратите неопределеното състояние.Това гарантира, че изходите остават стабилни и предсказуеми.Приложете логическа порта, която се намесва, когато S и R са едновременно високи (или ниски), коригирайки един вход за поддържане на валидно състояние.

Софтуерна симулация и хардуерно тестване

Провеждайте задълбочени софтуерни симулации, за да идентифицирате потенциални забранени състояния при различни работни условия.Това позволява на дизайнерите да забележат и коригират логически грешки преди физическото изпълнение.Извършете обширно хардуерно тестване, за да потвърдите, че веригата обработва правилно всички комбинации от вход.Тази стъпка помага да се гарантира, че фиксаторът или флип-флоп работят надеждно в сценарии в реалния свят.

Заключение

Универсалността и надеждността на SR ключалките подчертават тяхното значение в дизайна на цифровите вериги.Изследвайки нюансираното поведение на ключалките на SR чрез техните символни представи, таблици за истината и практически приложения, ние получаваме цялостно разбиране за тяхната работа и значение.Въпреки потенциалните клопки на неофинирани състояния в асинхронните дизайни, стратегическото прилагане на контролната логика и обширната симулация може да смекчи тези рискове.Инструментите за усъвършенствана електронна автоматизация на дизайна (EDA) допълнително подобряват надеждността и работата на веригите, включващи резюмета на SR, като прогнозират и разрешават проблемите на времето и синхронизацията.Независимо дали се използва във временното съхранение на данни, поддържането на контролния сигнал или откриването на грешки, SR Latches се оказват основополагащи при създаването на стабилни и ефективни цифрови системи.Тяхната роля в високоскоростните операции на паметта и синхронната обработка на данни в сложни приложения илюстрира тяхната трайна релевантност.С напредването на технологиите принципите, регулиращи Latches SR, продължават да информират и вдъхновяват иновации в цифровата електроника, като гарантират, че тези елементарни компоненти остават неразделна част от разработването на сложни и надеждни електронни устройства.

Често задавани въпроси [FAQ]

1. Какво е SR Latch?

SR резюме или резюме на Set-Reset е основен двоичен елемент за съхранение, използван в цифровите схеми.Това е асинхронна верига, което означава, че работи без часовник сигнал, разчитайки на директния контрол на входовете му за промяна на състоянията.

2. Каква е функцията на SR в логиката?

В логиката, SR (SET-RESET) входове контролират състоянието на ключалката.

3. Какъв тип логическа порта използва SR ключалката?

SR ключалката обикновено използва нито порти или порти на NAND.В SR Latch, базиран на NOR, изходът на всеки или порта се подава обратно във входа на другия, създавайки стабилен цикъл за обратна връзка.В NAND Gate-базирана SR Latch се използва подобна конфигурация за обратна връзка, но нивата на логиката са обърнати в сравнение с ключалката, базирана на GATE.И двете конфигурации постигат една и съща основна функционалност за поддържане на двоично състояние въз основа на набора и нулиране на входовете.

4. Как работи ключалката?

Резюме работи, като използва обратна връзка, за да поддържа изходното си състояние въз основа на предоставените входове.В SR резюме, наборът (ите) и нулиране (R) входове контролират състоянието на изхода (q).Когато зададеният вход е активиран (висок), изходът е зададен на висок (1).Когато входът за нулиране е активиран (висок), изходът се нулира до ниско (0).Оглъчът за обратна връзка в дизайна на ключалката гарантира, че след като бъде установено изходно състояние, той остава стабилен, докато нов входен сигнал го промени.

5. Какъв е недостатъкът при SR Latch?

Основният недостатък на SR ключалката е неопределеното състояние, което възниква, когато и двата набор (и), и нулиране (R) входове са високи едновременно.Това условие води до неопределено изходно състояние, което може да причини нестабилност и непредсказуемо поведение в цифровите схеми.Това „забранено“ състояние трябва да се избягва в дизайна, за да се осигури надеждна работа.

SR LATCH, Задаване на настройките, асинхронна верига, двоичен елемент за съхранение, цифрови вериги, нито порти, порти на NAND, цикъл за обратна връзка, високо състояние, ниско състояние, неопределено състояние, сигнал на часовника, директно управление, временно съхранение на данни, междинно задържане на резултата,Откриване на грешки, аерокосмически приложения, медицински изделия, дизайн на веригата, таксон на SR, входни сигнали, символ и структура, високоскоростна памет, буфери за данни, контрол на времето, прецизно управление, задържане на състоянието, микропроцесори, процесори на цифрови сигнали, вземане на проби от данни, даннисъхранение, задействано от ръба, флип-флоп на SR, заключваща обратна връзка, условия на състезание, логика на комуникационния протокол, синхронизация на рамката, откриване на грешки, сигнални проблеми, автоматизация на електронния дизайн, инструменти на EDA, механизми за синхронизация, управление на часовника, управление на времето, грешки в пропагацията, закъснение, закъснения, закъснения, закъснения, закъснения, закъснения на разпространението,Условия на състезанието, сложни трансфери на данни, системи за управление на захранването, механично отскачане, практически приложения, цифрови системи за управление, логически порти, софтуерни симулации, хардуерно тестване, забранени състояния, надеждност на ключалката.

За нас

ALLELCO LIMITED

Прочетете още

Бързо запитване

Моля, изпратете запитване, ние ще отговорим незабавно.

Ръководство за основите на джапанките - схеми, таблици за истината, видове, предимства и ограничения

на 2024/05/17

Сравнително ръководство за анализ на реостат и потенциометри

на 2024/05/17

Популярни публикации

-

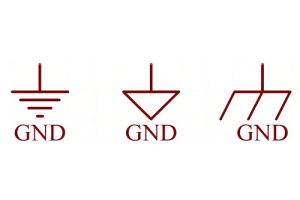

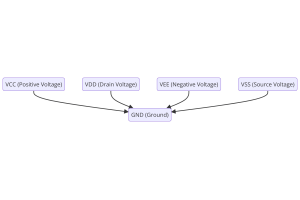

Какво е GND във веригата?

на 1970/01/1 2937

-

Ръководство за конектор RJ-45: RJ-45 Connector Color кодове, схеми за окабеляване, R-J45 приложения, RJ-45 таблици с данни

на 1970/01/1 2501

-

Видове конектори за влакна: SC срещу LC и LC срещу MTP

на 1970/01/1 2089

-

Разбиране на напреженията за захранване в Electronics VCC, VDD, VEE, VSS и GND

на 0400/11/9 1893

-

Сравнение между DB9 и RS232

на 1970/01/1 1763

-

Какво е батерия LR44?

Електричеството, тази повсеместна сила, тихо прониква във всеки аспект от ежедневието ни, от тривиални джаджи до животозастрашаващо медицинско оборудване, тя играе мълчалива роля.Въпреки това, наистина схващането на ...на 1970/01/1 1713

-

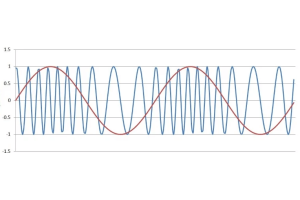

Разбиране на основите: Съпротива на индуктивността и заден план

В сложния танц на електротехниката трио от основни елементи заема централна сцена: индуктивност, съпротива и капацитет.Всеки носи уникални черти, които диктуват динамичните ритми на електронните вериги.Тук ние тръгва...на 1970/01/1 1655

-

CR2430 Изчерпателно ръководство за батерията: Спецификации, приложения и сравнение с CR2032 батерии

Какво е CR2430 батерия?Предимства на батериите CR2430НормаCR2430 Приложения на батериятаCR2430 еквивалентCR2430 срещу CR2032Размер на батерията CR2430Какво да търсите, когато купувате CR2430 и еквивалентитеЛист с данни PDFЧесто задавани въп...на 1970/01/1 1553

-

Какво е RF и защо го използваме?

Технологията на радиочестотната (RF) е ключова част от съвременната безжична комуникация, което позволява предаване на данни на дълги разстояния без физически връзки.Тази статия се задълбочава в основите на RF, обяснява...на 1970/01/1 1538

-

CR2450 срещу CR2032: Може ли вместо това батерията да се използва?

Литиевите манганови батерии имат някои прилики с други литиеви батерии.Високата енергийна плътност и дългият живот на експлоатацията са общите характеристики, които имат.Този вид батерия спечели доверието и благоскл...на 1970/01/1 1512