Разбиране на силата на ключалката S-R: шлюз към съвременната електроника

Latches са прости цифрови устройства, които съхраняват един бит информация и запазват тази стойност, докато не получат нови входни сигнали.Те се използват в цифрови системи за временно съхраняване на бинарни данни.Ключовете могат да бъдат направени с помощта на различни видове основни логически порти като и, или, не, NAND, и нито порти.Тази статия изследва дизайна, функцията, вариациите и използването на ключалката S-R, като подчертава най-добрата му роля в съвременната електроника и използването му в практически схеми и симулации на цифрови логики.

Каталог

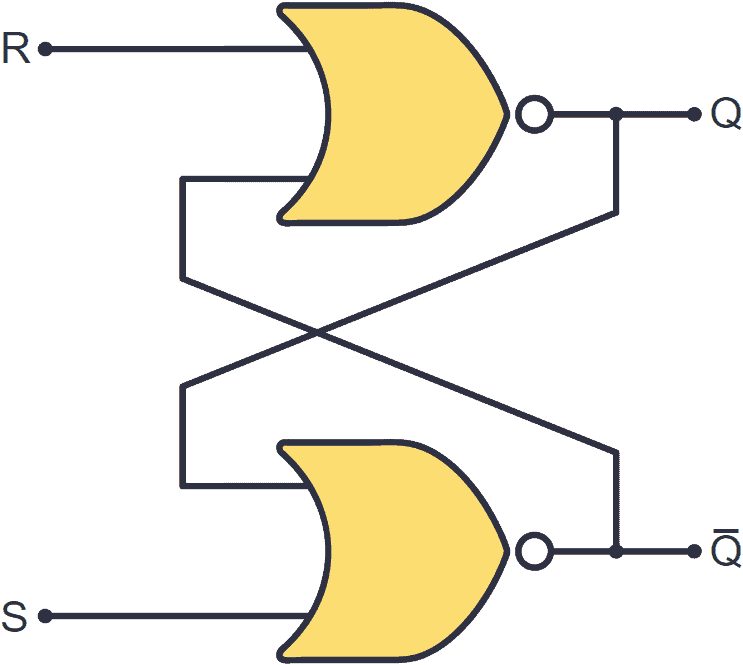

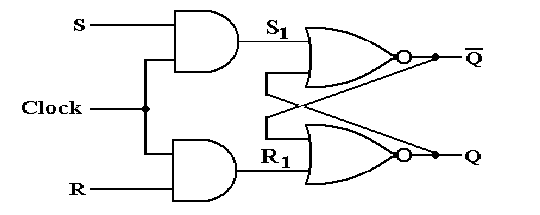

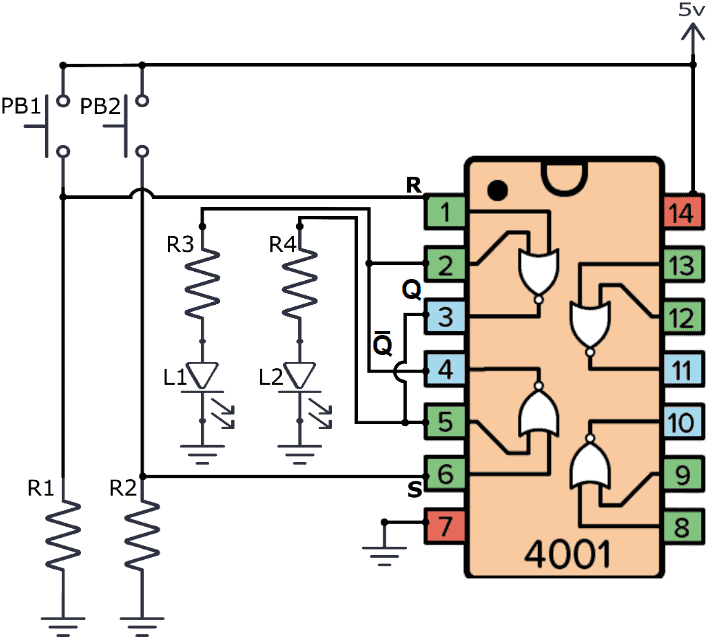

Фигура 1: Диаграма на S-R Latch

Структура на ключалката S-R

Записването на S-R (Set-Reset), крайъгълен камък в цифровата електроника, е бистабилен мултивибратор.Той е способен да поддържа едно от двете различни, стабилни състояния за неопределено време без външен вход.Тази функционалност прави SR Latch основен компонент в операциите за съхранение и превключване на паметта на различни електронни устройства.

Структурно, SR Latch се състои от две взаимосвързани, нито порти, подредени в конструкция на контура за обратна връзка.Това специфично споразумение има значение, тъй като предлага предпоставките за бистабилност.Изходът на всеки NOR GATE е свързан директно към входа на другия, създавайки непрекъснат цикъл от обратна връзка, която е в основата на операцията на ключалката.

Фигура 2: S-R ключалка и сигналът на часовника (CLK)

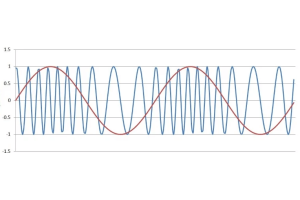

Разширявайки се на основния дизайн, затворенът SR Latch въвежда допълнителен, вход: сигналът на часовника (CLK).Това подобрение включва вход на часовника, който носи слой контрол, интегрирайки операциите на ключалката в системи, които изискват синхронизация.Тази синхронизация се задължава, тъй като определя точните моменти, когато ключалката може да промени състоянията, подходящо описани от термина „затворен“.Включването на сигнала на часовника гарантира, че промените в изходното състояние на ключалката се появяват само по време на фазата на активния часовник, обикновено при нарастващия или падащия ръб на CLK сигнала.

Въвеждането на входа на CLK не само запазва свойствата на основния SR ключалка, но също така привежда в съответствие с работата му с времевата динамика на по -големите цифрови системи.Това желание за подравняване за поддържане на целостта на данните и гарантиране, че преходите на състоянието се случват без проблеми или непредвидени промени, особено в сложни конфигурации на веригата, където могат да си взаимодействат множество ключалки.Като контролира кога ключалката реагира на командите на множеството и нулиране, системата може да избегне проблеми като условия на състезание и други грешки, свързани с времето, които в противен случай биха могли да нарушат стабилността и производителността на системата.

Оперативни състояния на ключалката S-R

Работата му зависи от входовете на два контролни сигнала: набор (и) и нулиране (R).Тук обясняваме как тези входове влияят на изходите и състоянията на SR ключалката.

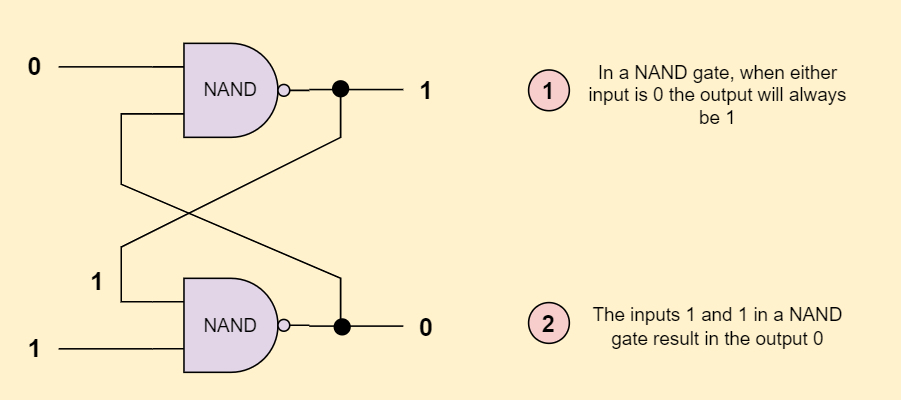

Случай 1: Задайте условие

Когато входът (и) вход е висок (1) и входът за нулиране (R) е нисък (0), резето влиза в зададеното състояние.В това състояние NAND портата, свързана с R входа, ще изведе нисък сигнал поради високия вход от S. Този нисък сигнал причинява втората NAND порта към извеждане на висок сигнал, задаване на Q на висок (1) и Q-BARдо ниско (0).Това състояние е стабилно и ще поддържа Q високо, докато входовете не се променят, показвайки способността на ключалката да съхранява високо състояние.

Фигура 3: Състоянието на зададеното

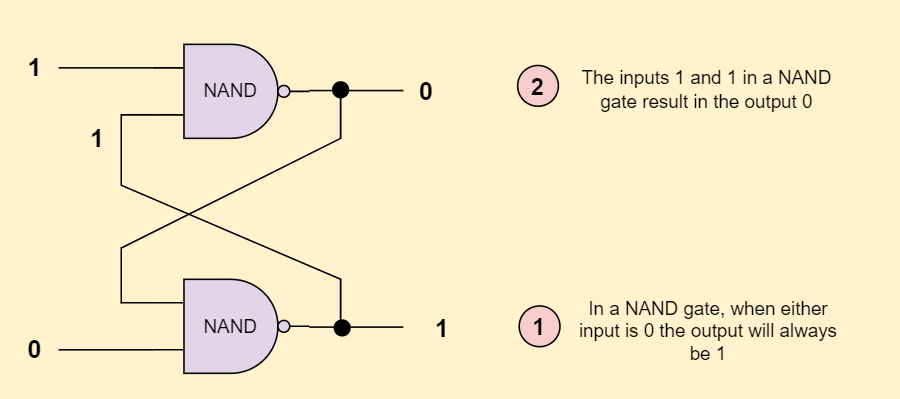

Случай 2: Състояние на нулиране

Когато S е ниско (0), а R е висок (1), резето влиза в състоянието на нулиране.Тук високият вход на R и ниският вход на S правят NAND портата свързана към R изход с нисък сигнал.Този нисък сигнал задава Q до ниско (0) и q-бар до висок (1), ефективно нулира резето.Това демонстрира способността на ключалката да се върне в стабилно ниско състояние в Q, когато се получат правилните входове.

Фигура 4: Състоянието на нулиране

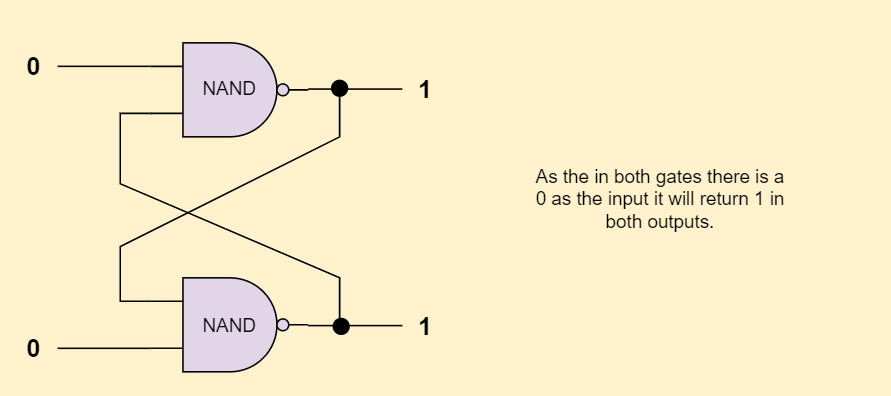

Случай 3: Невалидно състояние

Ако и S, и R са ниски (0), и двата входа към NAND портите са ниски, което води до високи изхода Q и Q-Bar.Това състояние се нарича невалидно или забранено, тъй като нарушава основното правило, че Q и Q-Bar винаги трябва да бъдат противоположности.Този сценарий подчертава ограничаването на ключалката на SR, като подчертава важността на избягването на такива нестабилни състояния чрез правилното управление на входа.

Фигура 5: Невалидното състояние

Случай 4: Условие за задържане

Когато и двата входа са високи (1), изходите зависят от предишното състояние на ключалката, а не от текущите входове.Това е известно като условие за задържане, където Q и Q-Bar остават непроменени, запазвайки последното валидно състояние на резето.За някои приложения е важно да можете да поддържате закопчатото състояние за дълги периоди от време без модификация, като например клетки за съхранение на памет, където целостта на данните е от голямо значение.

Фигура 6: Състоянието на задържане

S-R Latch с таблица за истината

Тази таблица не е просто теоретичен инструмент, но е практична както за дизайнерите на вериги, така и за студентите.Помага им да видят как ключалката се държи при много условия.По -долу представяме цялостната таблица за истината за SR Latch, последвана от обяснения и практически прозрения за всяко условие.

|

S |

R |

Q |

Q-bar |

Състояние |

|

0 |

0 |

1 |

1 |

Невалиден |

|

0 |

1 |

0 |

1 |

Нулиране |

|

1 |

0 |

1 |

0 |

Комплект |

|

1 |

1 |

Q |

Q-bar |

Задръжте |

Графика 1: SR

Latch Tight Table

Обяснение на всеки ред

Зададено условие (s = 1, r = 0): Този ред показва, че когато s е висок и r е нисък, Q е настроен на висок (1) и q-бар до нисък (0).Това отразява реакцията на веригата на зададена команда, като ефективно съхранява „1“.

Нулиране на условието (S = 0, R = 1): Тук входовете показват операция за нулиране.Следователно, Q се нулира до ниско (0) и Q-BAR е настроен на висок (1).Това състояние демонстрира капацитета на ключалката да се върне към „0“.

Невалидно условие (s = 0, r = 0): И двата изхода стават високи в това състояние, което обикновено се избягва, тъй като води до това, че и двете изхода са идентични.Това може да доведе до нестабилност или неопределено поведение в резето, тъй като нарушава правилото, че Q и Q-Bar винаги трябва да бъдат противоположности.

Задържане на условие (S = 1, R = 1): В този сценарий ключалката поддържа предишното си състояние, показвайки способността си да държи последното състояние, освен ако изрично не бъде заповядано да се промени.

Практически прозрения и съвети

Разбиране на резултатите: Винаги помнете, че Q и Q-Bar в идеалния случай са допълнени.Всяко отклонение от това правило (както се вижда в невалидното състояние) показва проблем или погрешно конфигуриране.

Избягвайки невалидното състояние: Задължително е дизайнерите да се погрижат да предотвратят ситуацията, в която S и R са ниски.Прилагането на допълнителна логика или блокировки може да помогне за предотвратяване на това състояние.

Използване на условието за задържане: Състоянието на задържане може да бъде особено удобно в приложения, изискващи съхранение на данни във времето.Поддържането на целостта на данните може да зависи от това да се гарантира, че резето не по невнимание влиза в състоянието на множеството или нулиране.

Тълкуване на таблицата за истината: Когато проектирате или отстранявате отстраняване на грешки, препратете таблицата за истината, за да предскажете как промените в входа ще се отразят на изхода, особено в сложни вериги, където се използват множество ключалки.

Функционална динамика на ключалката S-R

Записването на S-R (Set-Reset) работи добре само ако входовете му се управляват правилно.За да разберете как функционира, трябва да знаете как различните входни комбинации влияят на изходите, q и q-bar (обратното на Q).

Фигура 7: S-R ключалка

Ако и двата набор (и), и нулиране (r) се активират едновременно (s = 1 и r = 1), ключалката преминава в "забранено състояние", където и двата изхода, q и q-bar, са 0.Това е проблем, тъй като обикновено Q и Q-Bar трябва да са противоположности.

При нормални условия, за да зададете ключалката, вие активирате S (задайте S до 1) и деактивирайте R (Set R to 0).Това прави Q Go високо (1) и Q-Bar Go Low (0), показвайки, че ключалката може да съхранява 1. За да нулирате ключалката, активирате R (Set R до 1) и деактивирайте S (задайте s до 0).Това прави Q да ниско (0) и Q-Bar Go (1), показвайки, че ключалката може да се изчисти и да съхранява 0.

Когато и двата входа са деактивирани (s = 0 и r = 0), ключалката запазва последното си състояние, набор или нулиране.Това е добре за съхранение на данни или за съхраняване на състояние, без да се нуждаете от непрекъснат вход.

Условията на състезанието могат да усложнят работата на S-R Latch.Тези грешки се случват, когато изходите разчитат до голяма степен на времето на промените в входа, което води до непредвидими резултати, ако входовете се променят почти същото време.За да се предотврати това и да се гарантира, че ключалката работи надеждно, често се използват механизми за забавяне на времето.Тези закъснения се уверяват, че единият вход се активира, след като другият е имал време за стабилизиране.За да се използва резето в цифрови схеми, където се изисква прецизно време, тя трябва да се изпълнява последователно и да поддържа стабилни изходи.Това става възможно чрез контролираното време.

Логическа диаграма на S-R Latch

SR Latch е основна последователна логическа схема с две основни конфигурации: нито порти на NAND.Всяка настройка влияе върху начина, по който резюмето работи и реагира на входовете, което позволява персонализиране на различни електронни приложения.

Фигура 8: Логическата диаграма представлява ключалката S-R с помощта на NAND Gate

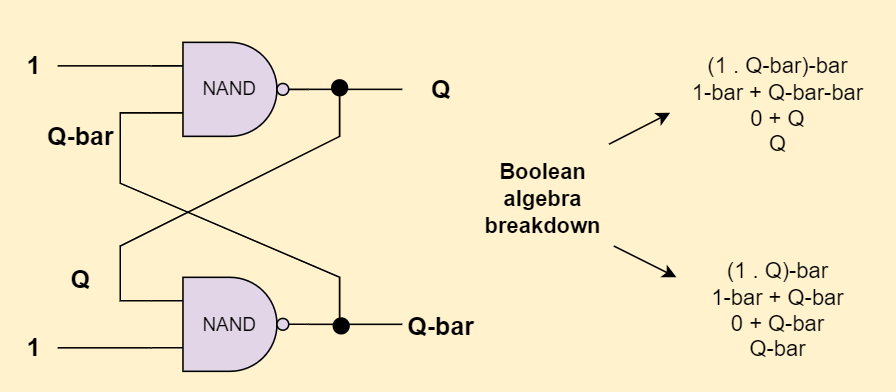

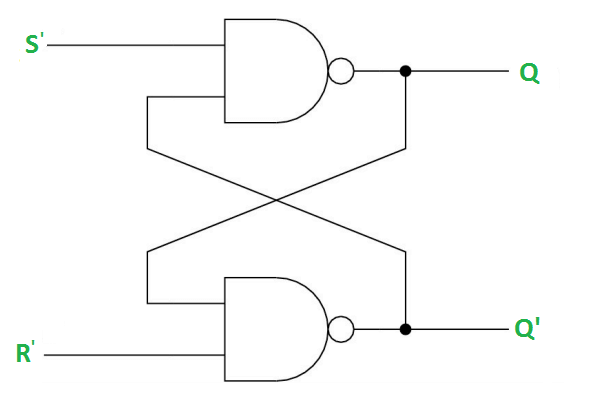

Изпълнение с помощта на NAND Gates

При изграждането на SR ключалка с NAND Gates се използва цикъл за обратна връзка за поддържане на състоянието му.Тази настройка позволява на ключалката да запази предишното си състояние, когато и двата входа (S и R) са ниски.NAND Gates изхожда високо, освен ако и двата входа не са високи.Състоянието на ключалката се променя, когато единият вход е висок, а другият е нисък.Най -добре е да избягвате да настроите едновременно S и R високо, защото това принуждава и двата изхода да намалеят, което води до неопределено състояние, където изходите вече не се допълват.Правилното управление на входа е задължително за предотвратяване на нестабилност в базираните на NAND SR-ключалки.

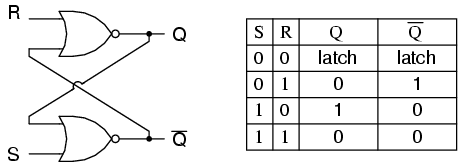

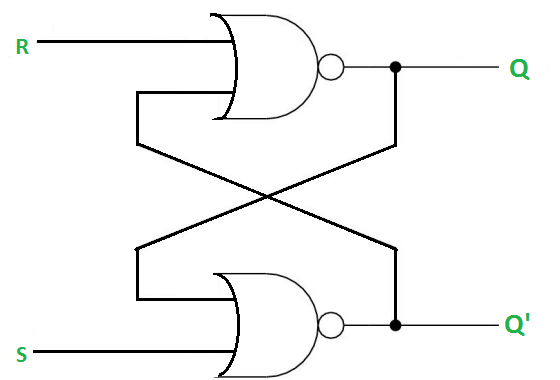

Изпълнение с помощта на нито порти

Използването на нито порти за SR Latch променя оперативните условия в сравнение с NAND Gates.В тази конфигурация ключалката държи състоянието си, когато и двата входа са високи.Резето се променя състоянието, когато единият вход е нисък, а другият е висок.Нито портите изхождат високо само ако и двата входа са ниски.Тази настройка е полезна в вериги, където състоянието по подразбиране трябва да има ниски изхода, като гарантира предвидим изход при условия с висока входа.Най -добре е обаче да избягвате да настроите двата входа едновременно едновременно, тъй като това причинява противоречиви резултати и намалява надеждността на ключалката.

Фигура 9: Логическата диаграма представлява S-R Latch с помощта на NOR GATE

Примерна верига

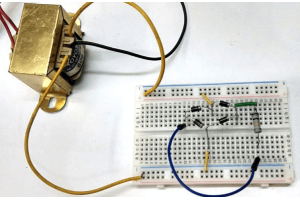

Проучването на това как работят SR реколтата в реалния живот показва тяхната полезност.Добър пример е верига, използваща чипа CD4001, който има четири нито порти.Тази схема показва как SR ключалките могат да контролират устройства като светодиоди с прости действия като натискане на бутони.

В този пример са настроени портите NOR в чипа CD4001, за да направят SR капак.Две порти са свързани в контур за обратна връзка, за да се запази състоянието на ключалката.Бутоните се добавят към веригата като входове за набор и нулиране.Натискането на бутон променя състоянието на входа, което променя ключалката и LED състояние.Например, натискането на бутона SET светва светодиода и той остава осветен дори след пускането на бутона, показвайки как ключалката може да запази състояние.

За да се направи схемата по-добра, могат да се добавят повече светодиоди, за да се покаже изходното състояние както на Q, така и на Q-BAR.Това улеснява виждането как работи ключалката, което е много полезно в учебната среда.

Фигура 10: S-R Latch с помощта на чипа CD4001

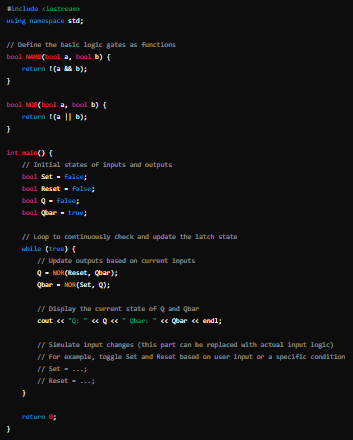

Изпълнение на код

Превеждането на оперативната логика на SR Latch в софтуер показва как дигиталният логически дизайн може да работи както в хардуер, така и във виртуални симулации.Използването на език за програмиране като C ++ е ефективно, тъй като поддържа сложната логика и контрол, необходими за имитиране на хардуерно поведение.

За да направите SR Latch в C ++, започвате с дефинирането на основните логически порти като функции, които действат като техните хардуерни версии.Например, функцията на NAND Gate ще върне обратното на и работата на своите входове.По същия начин, функция на портата ще върне обратното на операцията или операцията.С тези основни функции можете да моделирате поведението на SR Latch, като създадете контур за обратна връзка между тези функции на портата въз основа на схемата на веригата на ключалката.

Кодът обикновено има цикъл, който непрекъснато проверява състоянията на входовете (задайте и нулира) и съответно актуализира изходите (q и q-bar).Условните изявления вътре в този цикъл определят как промените в входа влияят на изходите, като отблизо имитирането на физическото поведение на SR Latch.Например, ако и входовете на зададения, и нулиране са ниски, изходите остават същите.Ако наборът е висок и нулирането е ниско, изходът Q става висок и Q-BAR става нисък, репликирайки зададеното условие на резето.

Ето един прост пример за това как може да изглежда това в кода:

Фигура 11: SR Latch в C ++

Този код създава обикновен SR ключалка, използвайки нито порти и непрекъснато проверява и актуализира състоянието на ключалката въз основа на входовете.

Приложения на SR ключалката

Системи за управление в двигателните операции: SR капака, изисквана от системите за управление на двигателя.Използвайки стартиране (и) и спиране (R) бутон бутон, SR Latch поддържа двигател, който работи дори след пускането на бутона за стартиране.Тази настройка гарантира, че двигателят работи непрекъснато, докато не се спре, повишавайки безопасността и удобството.

Памет и съхранение на данни: Когато създавате по -големи схеми на паметта, SR ключалката играе роля, тъй като може да съхранява един бит данни.Той поддържа данни в стабилно състояние до актуализиране, формирайки основата на клетките на паметта в цифровите изчисления.

Контрол и управление на сигнала: В приложенията за контрол на сигнала, SR ключалките държат специфични битове, докато не бъдат изпълнени определени условия, осигурявайки правилна последователност и време в операциите.Прецизността в обработката на сигнала и потока на данните зависят от това.

Debouncing Circuits: SR Latches стабилизират сигналите от механични превключватели и бутони, предотвратявайки фалшиво задействане и грешки, причинени от "отскачането" при натискане на превключвателите.Това е особено подходящо в цифрови интерфейси като клавиатури.

Основни елементи в цифровите системи: Дизайнът на джапанки и броячи, които са подходящи за време и секвениране в електрониката, разчита до голяма степен на SR ключалки.Те се използват и като импулсни ключалки за бързо превключване на състоянието.

Специализирани приложения: В асинхронните системи вариациите като D фиксацията се използват за защитен и надежден трансфер на данни.В синхронни двуфазни системи, ключалките на данни намаляват броя на транзита, подобряват ефективността и намаляват забавянето.

По -широки последици при електрониката: SR ключалките се използват широко в схемите за захранване, играейки роля в енергийното опазване в рамките на електронните устройства.Те управляват състоянията на захранването на подробно ниво, допринасяйки за цялостната енергийна ефективност на цифровите системи.

Заключение

Завъртането на S-R показва важността на прости логически структури в сложни цифрови системи.Разглеждайки различните му настройки и как работи, виждаме, че S-R Latch поддържа данните стабилни и прави системите ефективни и надеждни.Той може да работи при различни условия, показани от таблици за истината и логически диаграми, което го прави адаптивен за няколко приложения, от двигателно управление до основни цифрови схеми като джапанки и броячи.Закрепването на S-R е подходящ в много практически приложения, като клетки на паметта в компютри и дебюниращи вериги в цифрови интерфейси, повишаване на ефективността и намаляване на грешките в електронните устройства.С механизмите за обратна връзка и внимателното управление на входните сигнали, S-R ключалката е добра за проектиране на по-надеждни и ефективни цифрови системи.Изучаването на неговата функция чрез софтуерни симулации помага да се свърже теоретичната електроника с приложения в реалния свят, което прави S-R Latch важна тема както за нови, така и за опитни електронни инженери.

Често задавани въпроси [FAQ]

1. Каква е целта на SR ключалката?

SR ключалката се използва за съхраняване на един бит данни;Това е основна форма на памет в цифровите схеми.Основната му функция е да запази състоянието на малко, докато не бъде променено чрез входни сигнали.

2. SR Latch активен ли е висок или нисък?

SR ключалката обикновено е активна високо, което означава, че реагира на високи входове (ниво на логика 1).Когато входовете s (set) и r (нулиране) са високи, те задействат промени в изхода.

3. Какъв е недостатъкът при SR Latch?

Основен недостатък на ключалката на SR е неговата чувствителност към невалидно състояние, при което и входовете на набора и нулиране са високи едновременно.Тази ситуация води до неопределен изход, което може да доведе до ненадеждно или непредсказуемо поведение.

4. Какви са правилата за ключалката на SR?

Ако S (Set) е висок и R (нулиране) е нисък, изходът Q е настроен на висок.

Ако R е висок и S е нисък, изходът q се нулира до ниско.

Ако и S, и R са ниски, изходът запазва предишното си състояние.

Ако и S, и R са високи, изходът е неопределен или невалиден.

5. Какво е паметта в SR Latch?

Паметта в резюме на SR се отнася до способността му да поддържа изходното състояние (високо или ниско) за неопределено време, докато не получи вход за промяна на състоянието.Това го прави бистабилно устройство, идеално за просто съхранение на паметта.

6. Какви са резултатите от SR ключалката?

SR ключалката има два изхода, Q и Q '(Q-BAR).Q представлява текущото състояние, докато Q 'е обратната на Q. Когато Q е висок, Q' е нисък и обратно.

7. Къде използваме Latch?

Когато се изискват краткосрочно съхранение на данни или задържане на състоянието, ключалките се използват в различни видове приложения.Това включва съхранение на данни в джапанки, регистри и агрегати на паметта, както и в системи, изискващи синхронизиране на данни и функции за задържане на вериги.

За нас

ALLELCO LIMITED

Прочетете още

Бързо запитване

Моля, изпратете запитване, ние ще отговорим незабавно.

Статично електричество

на 2024/06/19

Гръбнакът на електрическите системи: цялостно ръководство за токоизправители

на 2024/06/17

Популярни публикации

-

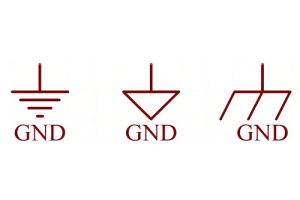

Какво е GND във веригата?

на 1970/01/1 2943

-

Ръководство за конектор RJ-45: RJ-45 Connector Color кодове, схеми за окабеляване, R-J45 приложения, RJ-45 таблици с данни

на 1970/01/1 2501

-

Видове конектори за влакна: SC срещу LC и LC срещу MTP

на 1970/01/1 2089

-

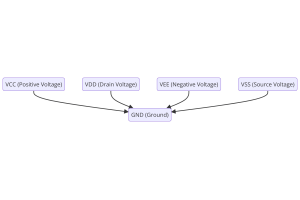

Разбиране на напреженията за захранване в Electronics VCC, VDD, VEE, VSS и GND

на 0400/11/9 1895

-

Сравнение между DB9 и RS232

на 1970/01/1 1765

-

Какво е батерия LR44?

Електричеството, тази повсеместна сила, тихо прониква във всеки аспект от ежедневието ни, от тривиални джаджи до животозастрашаващо медицинско оборудване, тя играе мълчалива роля.Въпреки това, наистина схващането на ...на 1970/01/1 1714

-

Разбиране на основите: Съпротива на индуктивността и заден план

В сложния танц на електротехниката трио от основни елементи заема централна сцена: индуктивност, съпротива и капацитет.Всеки носи уникални черти, които диктуват динамичните ритми на електронните вериги.Тук ние тръгва...на 1970/01/1 1655

-

CR2430 Изчерпателно ръководство за батерията: Спецификации, приложения и сравнение с CR2032 батерии

Какво е CR2430 батерия?Предимства на батериите CR2430НормаCR2430 Приложения на батериятаCR2430 еквивалентCR2430 срещу CR2032Размер на батерията CR2430Какво да търсите, когато купувате CR2430 и еквивалентитеЛист с данни PDFЧесто задавани въп...на 1970/01/1 1555

-

Какво е RF и защо го използваме?

Технологията на радиочестотната (RF) е ключова част от съвременната безжична комуникация, което позволява предаване на данни на дълги разстояния без физически връзки.Тази статия се задълбочава в основите на RF, обяснява...на 1970/01/1 1542

-

CR2450 срещу CR2032: Може ли вместо това батерията да се използва?

Литиевите манганови батерии имат някои прилики с други литиеви батерии.Високата енергийна плътност и дългият живот на експлоатацията са общите характеристики, които имат.Този вид батерия спечели доверието и благоскл...на 1970/01/1 1512