EP2S60F672C4 FPGA: Функции, приложения, Ръководство за програмиране и данни

В това ръководство ще получите ясен преглед на EP2S60F672C4, мощен FPGA от семейството на Stratix II на Intel.Ще научите за основните му характеристики, архитектурата, структурата на блока и техническите характеристики, за да разберете как се вписва в модерни цифрови дизайни.Освен това ви превежда през своите стъпки за програмиране, приложения, предимства и недостатъци, за да можете да видите къде точно и как това устройство може да се използва.Каталог

Какво е EP2S60F672C4?

The EP2S60F672C4 е FPGA с висока плътност от Intel (преди Altera), принадлежащ към семейството на Stratix II.Изграден на 90 nm, 1.2 V Copper SRAM процес, той осигурява значителен логически капацитет в рамките на FBGA пакет с мощност 672, което го прави идеален за сложни цифрови системи.Като част от серията EP2S устройството „60” седи в средния до горния диапазон на състава на Stratix II, предлагайки силен баланс на логическата плътност, вградената памет и I/O ресурсите.Известен със своята здрава архитектура и надеждност, тази FPGA остава надежден избор в много напреднали дизайни.

Търсите EP2S60F672C4?Свържете се с нас, за да проверите текущите запаси, времето за изпълнение и ценообразуването.

EP2S60F672C4 CAD модели

EP2S60F672C4 символ

EP2S60F672C4 Отпечатък

EP2S60F672C4 3D модел

Функции EP2S60F672C4

• Разширени 90 nm, 1,2 V CMOS процес

EP2S60F672C4 е изработен при 90 nm изцяло сложен меден CMOS процес, който работи при 1,2 V основно напрежение.Тази технология позволява висока скорост, намалена консумация на енергия и по -голяма логическа плътност в сравнение с по -старите поколения на FPGA.

• Архитектура на адаптивен логически модул (ALM)

Устройството използва милостиня като своя логически градивен елемент вместо традиционните логически елементи.Тази архитектура подобрява използването на ресурси, което позволява по -сложни логически функции да се реализират ефективно в една и съща силиконова зона.

• Висока логическа плътност

С приблизително 60 440 логически елемента (24,176 милостиня), FPGA поддържа големи и сложни цифрови дизайни.Този висок капацитет го прави подходящ за приложения като обработка на сигнали, комуникации и вградени системи за управление.

• TriMatrix ™ памет на чипа

EP2S60F672C4 интегрира три вида RAM блокове, (M512, M4K и M-RAM), за да осигури общо около 2,4 mbits вградена памет.Този микс позволява да се прилагат малки FIFO, средни буфери и големи спомени с двойно порт.

• Специализирани DSP блокове

Устройството включва 36 специализирани DSP блока, предназначени за аритметични операции като умножения, натрупвания и FIR филтриране.Тези блокове повишават ефективността в изчислителните интензивни задачи, като същевременно спестяват общи логически ресурси.

• Високоскоростна входна/изходна цялост и целостта на сигнала

Той поддържа различни единични и диференциални I/O стандарти, заедно с динамично фазово подравняване (DPA) схема.Тези характеристики позволяват стабилен, високоскоростен пренос на данни до 1 Gbps, като гарантира надеждна комуникация с външни компоненти.

• Богата поддръжка на интерфейс за външна памет

FPGA е съвместим с DDR, DDR2, QDR II, RLDRAM II и други стандарти за памет.Вграденият интерфейс поддръжка опростява дизайна на дъската и постига висока пропускателна способност за данни за интензивни приложения на паметта.

• Гъвкаво управление на часовника

До 12 PLL на чип позволяват умножение на часовника, разделяне, изместване на фазата и превключване без проблем.Можете да прецизирате домейни на часовника и да намалите трептенето, поддържайки вътрешните честоти на часовника до 500–550 MHz.

• Битстрийм криптиране и преконфигуриране

EP2S60F672C4 поддържа AES-базирана битстрийм криптиране за осигуряване на интелектуална собственост.Той също така предлага отдалечена способност за преконфигуриране, което позволява актуализации в полето, без да се заменя устройството.

Сратикс II блокова диаграма

Диаграмата на Stratix II, както е показано за EP2S60F672C4, илюстрира вътрешното подреждане на логиката, паметта и DSP ресурсите, които формират сърцевината на FPGA.Логическите блокове (LABs) са подредени в обикновена решетка, заобиколена от вградени колони RAM и DSP, които осигуряват бързи възможности за аритметика и чип.Периферните входно -изходни елементи и часовниковите мрежи рамкират тази структура, като позволяват ефективен трансфер на данни и контрол на времето между FPGA и външните устройства.Тази диаграма е важна, защото помага да се разбере как различните функционални блокове са организирани физически, което им позволява да оптимизират поставянето, маршрутизирането и цялостната ефективност на системата.

Диаграма на банките Stratix II/O банки

Тази диаграма на банките Stratix II II илюстрира как са групирани входните/изходните щифтове на EP2S60F672C4 и какви електрически стандарти поддържат всяка група.Всяка банка I/O е проектирана да обработва специфични нива на напрежение, типове сигнали и функции като LVTTL, SSTL, LVDS или стандарти за въвеждане на часовник.Оформлението показва как различните банки (напр. 1, 2, 5, 6 срещу 3, 4, 7, 8 и т.н.) са оптимизирани или за обща граница в I/O, или за високоскоростна диференциална сигнализация, включително поддръжка за входове на LVDS/LVPECL Clock в краищата.Разбирането на тази структура е важно при присвояване на пинове, тъй като правилният избор на банка гарантира електрическа съвместимост, опростява маршрутизирането на борда и увеличава максимално производителността на FPGA във високоскоростни дизайни.

Спецификации на EP2S60F672C4

|

Тип |

Параметър |

|

Производител |

Altera/intel |

|

Серия |

Stratix® II |

|

Опаковане |

Табла |

|

Статус на част |

Остарял |

|

Брой лаборатории/CLB |

3022 |

|

Брой логически елементи/клетки |

60,440 |

|

Общи битове на RAM |

2,544,192 |

|

Брой на I/O. |

492 |

|

Напрежение - захранване |

1.15 V ~ 1,25 V |

|

Тип монтаж |

Повърхностно монтиране |

|

Работна температура |

0 ° C ~ 85 ° C (TJ) |

|

Пакет / случай |

672-BBGA |

|

Пакет устройства за доставчици |

672-FBGA (27 × 27) |

|

Основен номер на продукта |

EP2S60 |

Приложения EP2S60F672C4

1. Обработка на цифрови сигнали (DSP) и филтриране

EP2S60F672C4 е много подходящ за внедряване на високоефективни DSP функции като FIR и IIR филтри, FFT обработка и сложни аритметични операции.Специалните му DSP блокове се справят ефективно с умножнения и натрупвания, освобождавайки общите логически ресурси за други задачи.Паметта на Chip Trimatrix ™ позволява гладко буфериране на данни и тръбопровод, което е чудесно за обработка в реално време при високи скорости на пробата.Това прави устройството идеално за усъвършенствани приложения за аудио, видео и радар.

2. Високоскоростна комуникация и работа в мрежа

Високоскоростните I/O интерфейси и динамичното фазово подравняване на FPGA (DPA) поддържат надеждно, предаване на данни на ниво гигабит.Той може да внедри комуникационни протоколи и функции на физически слоеве за системи като маршрутизатори, превключватели и връзки на задните плоскости.С големия си логически капацитет и гъвкавите PLLs той може да управлява сложни времеви и протоколни преобразувания между множество високоскоростни интерфейси.Тези възможности го правят силно подходящ за телекомуникационната инфраструктура и мрежовото оборудване с висока лента.

3. Контролери за памет и системи за обработка на данни

EP2S60F672C4 поддържа различни интерфейси за външна памет, включително DDR, DDR2, RLDRAM II и QDR II, което го прави идеален за проектиране на контролери за памет с висока лента.Той може да обработва буфериране на данни, генериране на адреси и арбитраж при високи скорости с минимална латентност.Комбинацията от бързи часовници и вградени RAM блокове позволява ефективно управление на големи потоци от данни.Това прави FPGA подходящ за обработка на изображения, видео стрийминг и научни изчислителни платформи, които разчитат на голяма пропускателна способност.

4. Персонализирано логика и вградено ускорение

С над 60 000 логически елементи и богато управление на часовника, FPGA може да хоства персонализирани хардуерни ускорители за специфични алгоритми.Дизайнерите често го използват за разтоварване на изчислително интензивни задачи от процесори, като криптиране, обработка на протокол или контролни контури в реално време.Той също може да интегрира множество функционални блокове, което го прави подходящ за сложни SOC-подобни дизайни.Тази гъвкавост го прави ценен в приложения като индустриални автоматизация, системи за сигурност и аерокосмически блокове.

5. платформи за прототипиране и развитие на образованието

Устройството EP2S60 обикновено се намира в комплекти за разработка на FPGA, използвани за прототипиране, тестване и академични изследвания.Неговият баланс на логическия капацитет, броя на I/O и DSP възможностите позволяват на инженерите и студентите да прилагат и проверяват пълните системи на един чип.Той поддържа бърза итерация на цифровите дизайни, което позволява проверка на хардуера, преди да се ангажира с ASIC разработката.Много университети и лаборатории за научноизследователска и развойна дейност го използват за преподаване на усъвършенствани концепции за дигитален дизайн и обработка на сигнали.

EP2S60F672C4 подобни части

|

Спецификация |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

Семейство / сериал |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

|

Логически елементи (LE) |

60,440 |

60,440 |

60,440 |

60,440 |

60,440 |

60,440 |

|

Милостиня |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

24,176 |

|

Пакет |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

Степен на скорост |

C4 (STD) |

C3 (по -бързо) |

C5 (по -бързо) |

C5 (по -бързо) |

I4 (std) |

I3 (по -бързо) |

|

Температурна степен |

Търговски (0 ~ 70 ° C) |

Търговски |

Търговски |

Търговски |

Промишлено (-40 ~ 100 ° C) |

Промишлено (-40 ~ 100 ° C) |

|

I/O щифтове |

492 |

492 |

492 |

492 |

492 |

492 |

|

Памет на чипа |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

2.4 Mbit |

|

Основно напрежение |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

|

Ключова разлика |

Основна търговска скорост |

C3 Speed Bin, без олово „N“ |

Кошче за по -висока скорост |

Кошче за по -висока скорост, вариант „N“ |

Промишлена температура, същата плътност |

Индустриална, по-бърза скорост, без олово |

EP2S60F672C4 стъпки за програмиране

Преди да можете да използвате EP2S60F672C4 FPGA в дизайна си, трябва правилно да го конфигурирате с компилирания си битстрийм.Този процес включва подготовка на програмния файл, настройка на хардуерния интерфейс и гарантиране, че конфигурацията се зарежда правилно при захранване.

Стъпка 1: Създайте и компилирайте вашия дизайн

Започвате с разработването на вашия логически дизайн с помощта на софтуера Intel Quartus II.След като завършите дизайна, го компилирате, за да генерирате файл за програмиране (.sof или .pof) специално за устройството EP2S60F672C4.Процесът на компилация проверява за времето, задачите на ПИН и използването на ресурси, за да се гарантира, че вашият дизайн се вписва в архитектурата на FPGA.След като бъде компилиран, вашият битстрийм е готов за конфигуриране на устройството.

Стъпка 2: Настройте хардуера за програмиране

След това подготвяте интерфейса за физическо програмиране между вашия компютър и FPGA дъската.Обикновено това включва свързване на USB-Blaster или съвместим JTAG кабел към JTAG порта на устройството.Трябва да проверите, че Quartus II разпознава програмиста и че целевото устройство е правилно открито.Тази стъпка гарантира стабилна комуникация преди започване на процеса на конфигуриране.

Стъпка 3: Заредете файла за програмиране в устройството

Използвайки инструмента за програмист Quartus II, добавяте компилирания .sof или .pof файл и изберете EP2S60F672C4 от списъка с открити устройства.След това инициирате последователността на програмиране, по време на която битстъм се прехвърля и зарежда в конфигурационните клетки на SRAM на FPGA.Трябва да следите лентата за прогрес и съобщенията за състоянието, за да потвърдите успешната конфигурация.След като бъде завършен, FPGA започва незабавно да изпълнява програмираната логика.

Стъпка 4: Проверете конфигурацията и работата

След програмиране проверявате дали устройството функционира по предназначение.Quartus II предоставя опция за проверка за проверка на конфигурацията CRC и сигналите на състоянието, като гарантира, че дизайнът се зарежда правилно.Можете също да тествате вашите I/O функции или да стартирате функционална симулация, за да потвърдите поведението на системата.Тази последна стъпка гарантира, че вашият дизайн е напълно работещ и стабилен на хардуера.

EP2S60F672C4 Предимства и недостатъци

Предимства

• Висока логическа плътност за сложни дизайни

• Добро съотношение между производителност и цена

• Лесна миграция в едно и също семейство

• Стабилни и зрели инструменти за развитие

• Доказана надеждност при индустриална употреба

Недостатъци

• остарял и по -труден за източник

• По -висока консумация на енергия от по -новите FPGA

• Няма модерни високоскоростни приемо-предаватели

• По -трудно затваряне на времето при високо използване

• Ограничена мащабируемост за бъдещи протоколи

EP2S60F672C4 Размери на опаковката

|

Тип |

Параметър |

|

Тип пакет |

672-FBGA (Fineline BGA) |

|

Размер на тялото (L × W) |

27,00 mm × 27,00 mm |

|

Обща височина на пакета (a) |

Макс 3,50 мм |

|

Височина на противопоставяне (A1) |

Мин 0,30 мм |

|

Дебелина на субстрата (A2) |

Макс 3,00 мм |

|

Диаметър на топката (B) |

0,50 mm - 0,70 mm |

|

Топка стъпка (д) |

1,00 mm |

|

Брой топки |

672 |

|

Монтажен стил |

Повърхностно монтиране |

|

Описание на пакета |

FBGA, 27 × 27 mm решетка |

EP2S60F672C4 Производител

EP2S60F672C4 FPGA се произвежда от Altera Corporation, водещ пионер в програмируеми логически устройства.През 2015 г. Altera е придобита от Intelи продуктът сега попада в програмируемите решения на Intel (PSG), която продължава да поддържа и доставя създадените FPGA семейства на Altera.Intel поддържа линията Stratix II като част от наследеното си продуктово портфолио, като гарантира документация, поддръжка на инструменти и дългосрочна наличност за индустриални и комуникационни приложения.

Заключение

EP2S60F672C4 комбинира висока логическа плътност, гъвкава архитектура на паметта и здрави функции на I/O за поддържане на сложни цифрови системи.Неговият базиран на ALM дизайн, Trimatrix ™ памет, DSP блокове и функции за управление на часовника позволяват ефективно внедряване на взискателни приложения.Въпреки че предлага доказана надеждност и зряла поддръжка за развитие, тя е изправена пред ограничения като остаряването и липсата на съвременни приемо -предаватели в сравнение с по -новите поколения на FPGA.Като цяло балансираната му производителност и гъвкавостта го правят солиден избор за обработка на сигнали, комуникация, обработка на данни и приложения за прототипиране.

DataSheet PDF

EP2S60F672C4 таблици с данни:

За нас

ALLELCO LIMITED

Прочетете още

Бързо запитване

Моля, изпратете запитване, ние ще отговорим незабавно.

често задавани въпроси [FAQ]

1. Може ли EP2S60F672C4 да работи със съвременни интерфейси за памет DDR?

Да, той поддържа интерфейсите DDR, DDR2, QDR II и RLDRAM II, които обхващат много общи стандарти за външна памет.Това го прави подходящ за приложения за обработка на данни с висока лента.

2. Изисква ли EP2S60F672C4 специална работа или съхранение?

Да, подобно на други компоненти, опаковани от BGA, той трябва да се съхранява в опаковки, контролирани от влага и да се обработва с защита на ESD.Следването на правилни практики за съхранение помага за поддържане на споразумеемост и надеждност на устройството по време на сглобяване.

3. Как можете да намалите консумацията на енергия в дизайна на EP2S60F672C4?

Можете да оптимизирате използването на логиката, неизползваните часовници, по-ниски I/O напрежения, когато е възможно, и да използвате опциите за синтез на мощност в кварта, за да сведете до минимум цялостното изтегляне на мощността.

4. Какви инструменти за програмиране са необходими за EP2S60F672C4?

Ще ви е необходим софтуер Intel Quartus II за дизайн, компилация и програмиране, заедно с USB-Blaster или съвместим JTAG кабел, за да конфигурирате устройството.

5. Поддържа ли актуализациите на EP2S60F672C4 или дистанционно преконфигуриране?

Да, той поддържа AES-базирана криптиране на битстрийм и дистанционно преконфигуриране, което ви позволява да актуализирате системата си сигурно, без физически да замените FPGA.

Всичко за LFXP6C-3FN256C решетка полупроводник

на 2025/10/6

XC2C256-7TQ144C CPLD: PINOUT, функции, ръководство за програмиране и данни

на 2025/10/3

Популярни публикации

-

Компютри на сложни инструкции: Как промениха изчисленията?

на 8000/04/19 147780

-

USB-C Pinout и функции

на 2000/04/19 112050

-

Използване на Xilinx Unified Simulation Primitives: Изчерпателно ръководство за FPGA дизайн и симулация

на 1600/04/19 111352

-

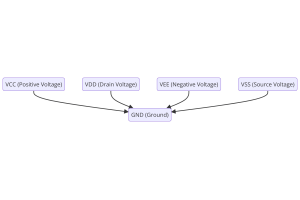

Захранващи напрежения в електрониката: Значение на VCC, VDD, VEE, VSS и GND

на 0400/04/19 83806

-

Ръководство за конектор RJ45: Pinout, окабеляване, видове кабели и употреби

на 1970/01/1 79608

-

Крайното ръководство за цветни кодове в съвременните електрически системи

Начинът, по който нашите електрически системи използват цветове, не е само за външен вид.Всеки цвят на проводника сега показва специфична функция, което улеснява идентифицирането и обработката на е...на 1970/01/1 66991

-

Ръководство за клапа на чист: функция, симптоми, тестване и подмяна на оптимална работа на двигателя

Клапанът на чистката е ключова част от системата на автомобила, която помага да се поддържа чистият въздух, като управлява изпаренията на горивото, преди да могат да избягат в атмосферата.Това не с...на 1970/01/1 63113

-

Качество (Q) Фактор: Уравнения и приложения

Коефициентът на качество, или „Q“, е важен при проверка на това колко добре работят индуктори и резонатори в електронни системи, които използват радиочестоти (RF).'Q' измерва колко добре веригата с...на 1970/01/1 63050

-

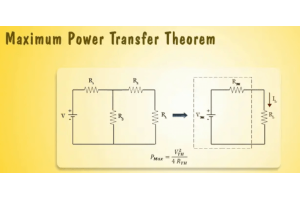

Постигане на пикова ефективност с теоремата за максимален трансфер на мощност

Теоремата за максимален пренос на мощност обяснява как енергия от източник, като батерия или генератор, преминава към свързан товар.Той показва точното състояние, при което товарът получава най -мн...на 1970/01/1 54097

-

Спецификации и съвместимост на батерията A23

Батерията A23 е малка батерия с форма на цилиндър с високо напрежение.Нарича се още 23A, 23AE или MN21, той работи на 12 волта и много по -високо от батериите на AA или AAA.Специалният му ...на 1970/01/1 52199