EPM7256AETC144-10N CPLD: Ръководство за данни, спецификации, приложения и програмиране

EPM7256AETC144-10N е програмируемо логическо устройство (CPLD) от серията Max® 7000A на Intel.Този чип е предназначен за бърза производителност, работещ с до 172.4 MHz със закъснение с 10 ns.Това ръководство обяснява всичко за този CPLD, включително неговите характеристики, спецификации, употреби, как да го програмирате и неговото оформление на ПИН.Ако имате нужда от надежден, програмируем чип за цифрови схеми, тази статия ще ви помогне да разберете как работи.Каталог

EPM7256AETC144-10N Описание

The EPM7256AETC144-10N е високоефективен CPLD от серията Max® 7000A на Intel, пригодена за взискателни задачи за интеграция на логиката.Това устройство може да се похвали с 256 макрокела и около 5000 използваеми порти, което улеснява значителната гъвкавост и полезността на проектирането в сложни цифрови среди.Работейки с максимална честота от 172,4 MHz със забавяне на разпространението само 5,5 ns, тя е проектирана за бърза работа.Проектиран с 3,3V работно напрежение и опаковано в компактен 144-пинов тънък квадратен плосък пакет (TQFP), EPM7256AETC144-10N поддържа здрави изисквания за логика.EPM7256AETC144-10N използва базирана на EEPROM не-променлива конфигурационна памет, което позволява постоянно съхранение на данни за програмиране.Тази функция, комбинирана с програмността на системата чрез интерфейса JTAG, осигурява лекота в актуализациите и препрограмирането на полето, подобрявайки дългосрочната използваемост без нужда от физическа преконфигуриране или подмяна.

Закрепете проектите си с надеждна, доказана в полето технология, като направите вашата насипна поръчка за EPM7256AETC144-10N с нас днес и гарантирайте, че имате солидно решение за CPLD.

CAD модели EPM7256AETC144-10N

EPM7256AETC144-10N Символ

EPM7256AETC144-10N Отпечатък

EPM7256AETC144-10N 3D модел

Функции EPM7256AETC144-10N

Макрокели:Това устройство е оборудвано с 256 макроклета.Макрокелите са конфигурируемите логически компоненти, които позволяват на CPLD да изпълнява различни логически функции.

Използваеми порти:Той осигурява приблизително 5000 използваеми порти.Това се отнася до еквивалентното количество основни логически порти (като и, или, не), които могат да бъдат конфигурирани в устройството.

I/O щифтове:CPLD разполага с 120 входни/изходни пина, които позволяват широко взаимодействие с други части на електронния дизайн на потребителя.

Забавяне на разпространението (TPD):Максималното забавяне на разпространението е 10 наносекунди, определяйки колко бързо CPLD може да обработва входни сигнали и да произвежда изходи.

Работна честота:Той може да работи с честоти до 95.2 MHz, което определя скоростта, с която устройството може да изпълнява логическите операции.

Захранващо напрежение:Устройството работи при захранващо напрежение от 3.3V, като се привежда в съответствие с обикновените нива на цифрова логика с ниско напрежение.

Пакет:Той се предлага в 144-пинов тънък квадратна плоска пакет (TQFP), компактен тип пакет, който е благоприятен за минимизиране на пространството, необходимо на отпечатаните платки.

Работен температурен диапазон:Диапазонът на работна температура е от 0 ° C до 70 ° C, което гарантира надеждна работа при широк спектър от условия на околната среда.

Програмируемост в системата:CPLD поддържа програмируемост в системата чрез IEEE STD.1149.1 Интерфейс на съвместна тестова група (JTAG), който позволява програмиране и препрограмиране на логическото устройство в рамките на крайната хардуерна конфигурация.

EPM7256AETC144-10N Блок-диаграма

The EPM7256AETC144-10N е a Сложно програмируемо логическо устройство (CPLD) с четири Логически блокове (лаборатории) , всяка от които съдържа 16 макроклета, общо 64 макроклета.Тези макроклетове се справят както с комбинираната, така и на последователната логика, което прави устройството гъвкаво за различни цифрови логически приложения.В центъра на CPLD е Програмируем масив за свързване (PIA), който свързва всички лаборатории, осигурявайки ефективно маршрутизиране на сигнала.Всяка лаборатория комуникира с PIA, използвайки 36 линии за свързване, което позволява да се споделят и обработват ефективно сигнали.Устройството разполага с контролни блокове от I/O от всяка страна, поддържайки 2 до 16 I/O пина на лаборатория.Тези блокове помагат за управление на функциите за вход и изход, свързвайки CPLD с външни вериги.Контролните сигнали като глобални часовници (GCLK1, GCLK2), изходът позволява (OE1) и глобалното нулиране (GCLRN) помагат да се синхронизират логическите операции в устройството.Освен това, логическите порти управляват часовника и нулират сигнали, като гарантират безпроблемна работа.Този CPLD е предназначен за високоскоростна обработка на логиката, предлагайки програмируемост, ефективно маршрутизиране на сигнала и надежден контрол на I/O, което го прави подходящ за вградени системи, комуникации и индустриална автоматизация.

Спецификации на EPM7256AETC144-10N

|

Тип |

Параметър |

|

Производител |

Altera/intel |

|

Серия |

Max® 7000a |

|

Опаковане |

Табла |

|

Статус на част |

Остарял |

|

Програмируем тип |

В системния програмируем |

|

Време за забавяне TPD (1) Макс |

10 ns |

|

Захранване на напрежението - вътрешно |

3V ~ 3.6V |

|

Брой логически елементи/блокове |

16 |

|

Брой макрокли |

256 |

|

Брой порти |

5000 |

|

Брой на I/O. |

120 |

|

Работна температура |

0 ° C ~ 70 ° C (TA) |

|

Тип монтаж |

Повърхностно монтиране |

|

Пакет / случай |

144-LQFP |

|

Пакет устройства за доставчици |

144-TQFP (20x20) |

|

Основен номер на продукта |

EPM7256 |

Приложения EPM7256AETC144-10N

Изкуствен интелект

Този CPLD се използва в хардуерните ускорители на AI, за да обработват сложни изчисления, необходими за ефективно обработка на AI алгоритми, подобрявайки както скоростта, така и надеждността в AI приложения.

5G технология

В сферата на 5G комуникациите EPM7256AETC144-10N е най-подходящ за обработка на сигнали и управление на комуникационни протоколи.Неговите високоскоростни логически операции улесняват бързата обработка, необходима при следващото поколение безжични системи.

Облачни изчисления

В рамките на центровете за данни това устройство подобрява възможностите за обработка, служейки като компонент за управление на големи обеми от данни и сложни изчисления, като подкрепя инфраструктурата на облачните услуги.

Потребителска електроника

CPLD намира приложения в потребителската електроника като телевизори и игрални конзоли, където изпълнява персонализирани логически функции, които подобряват функционалностите и опита на устройството.

Безжична технология

Използва се в безжичните комуникационни устройства за модулиране и демодулиране на сигнали, като гарантира ефективна и ефикасна комуникация в устройства като рутери и клетъчни модеми.

Индустриален контрол

Това устройство е неразделно за системите за автоматизация в индустриални настройки, където контролира машините и управлява процесите, допринасяйки за повишена производителност и безопасност.

Интернет на нещата (IoT)

В IoT устройства EPM7256AETC144-10N управлява задачите за обработка на данни и комуникация, чудесен за безпроблемната работа на свързани устройства в интелигентни домове и индустрии.

Медицинско оборудване

CPLD се прилага в медицински изделия за задачи като събиране на данни и обработка на сигнали, играейки роля в надеждността и ефективността на медицинската диагностика и оборудването за лечение.

EPM7256AETC144-10N Подобни части

EPM7256AETC144-10N предимства

Висока логическа плътност

Това устройство опакова 256 макроклета и приблизително 5000 използваеми порти, което позволява внедряването на сложни логически вериги в рамките на един чип.Тази висока логическа плътност улеснява по -интегрираните и компактни дизайни, намалявайки общия брой на компонентите и опростявайки оформлението на дъската.

Програмируемост в системата (ISP)

С участието на програмируемост в системата чрез IEEE STD.1149.1 JTAG интерфейс, EPM7256AETC144-10N позволява лесно програмиране и препрограмиране директно във веригата.Тази способност е безценна за бързо прототипиране и итеративни процеси на проектиране, което позволява да се правят корекции, без да се налага да се заменят чипа.

Бързо забавяне на разпространението

С максимално забавяне на разпространението от само 10 ns, този CPLD осигурява бърза обработка на входове и изходи за приложения, които изискват високоскоростно обработка на данни и навременни отговори, като например видео обработка и високочестотни системи за търговия.

Ниска консумация на енергия

Работейки на 3.3V захранващо напрежение, EPM7256AETC144-10N е оптимизиран за енергийна ефективност.Тази ниска консумация на енергия е полезна при преносими и батерии, при които управлението на мощността е добро за удължаване на експлоатационния живот.

Изчерпателни входно/изходно възможности

Устройството е оборудвано с 120 I/O пина, осигурявайки обширни опции за свързаност.Това позволява гъвкаво взаимодействие с широк спектър от периферни устройства и други компоненти на системата, което го прави силно адаптивен към сложните среди с много устройства.

Непрометащо съхранение на конфигурация

Благодарение на своята EEPROM базирана памет, CPLD запазва настройките си за конфигурация дори след изключване на захранването, гарантирайки, че функционалността на устройството остава последователна през мощните цикли.Тази функция е необходима за приложения, изискващи надеждна, дългосрочна производителност, без да е необходима честа преконфигуриране.

EPM7256AETC144-10N стъпки за програмиране

Програмирането на устройството EPM7256AETC144-10N включва шестстепенна програма за програмиране в системата (ISP):

1. Въведете ISP: Тази стъпка гарантира гладко входните и изходните части на превключвателя на устройството от нормална употреба към режим на програмиране.Отнема около 1 милисекунда.

2. Проверете идентификатора: Преди да започне програмиране, устройството проверява собствения си идентификатор.Тази стъпка е много бърза.

3. BULK ERASE: Това изчиства всички предишни данни от устройството.Това прави, като получи команда за изтриване на всичко и след това чака 100 милисекунди, за да се увери, че всичко е изтрито.

4. Програма: Тук се поставят новите данни в устройството.За всяка част от данните се изпраща на правилния адрес в устройството и след това специален импулс гарантира, че се съхранява правилно.

5. Проверете: След програмиране устройството проверява дали всички данни се съхраняват правилно, като го прочетат обратно и го сравняват с това, което трябва да бъде.

6. Излезте от ISP: Тази стъпка превключва устройството обратно от режим на програмиране в режим на нормално използване.Това също отнема около 1 милисекунда.

Общото време, необходимо за програмиране, зависи от това колко дълго трае всеки импулс и колко бързи данни могат да се преместят в и извън устройството, което се влияе от скоростта на часовника за програмиране и колко данни има за обработка.Различните устройства могат да отнемат различни количества време, тъй като имат различни количества памет за програмиране.

EPM7256AETC144-10N пакет с диаграма

Диаграмата показва очертанията на пакета EPM7256AETC144-10N и номерирането на ПИН.Този чип се предлага в a TQFP-144 (тънък четворен плосък пакет със 144 пина), което означава, че има фини стъпки от всичките четири страни.Местоположението на ПИН 1 е маркирано с малка точка, а номерата на ПИН се увеличават обратно на часовниковата стрелка около пакета.Ключови референтни щифтове като щифт 1, щифт 37, щифт 73 и щифт 109 помагат за ориентация по време на сглобяване на PCB.Размерите на очертанията определят физическия размер на чипа, за да се гарантира правилното монтиране на ПХБ.Подреждането на Pinout позволява ефективно маршрутизиране на сигнала, което го прави подходящ за сложни логически приложения.EPM7256AE е част от серията Max 7000A CPLD, включваща 256 макроклета и програмируемост в системата.Суфикс -10n показва 10 ns скорост на скорост и пакет без олово.

EPM7256AETC144-10N Производител

EPM7256AETC144-10N е сложно програмируемо логическо устройство (CPLD), първоначално разработено от Altera Corporation, което по-късно е придобито от Intel Corporation През 2015 г. след придобиването, Intel стана официален производител на продуктовите линии на FPGA и CPLD на Altera, включително серията Max® 7000A, на която това устройство принадлежи.EPM7256AETC144-10N е проектиран за високоефективни приложения с ниска мощност, поддържащ програмируемост в системата (ISP) чрез JTAG (IEEE 1149.1).Въпреки че Intel наследява CPLD технологията на Altera, оттогава това устройство е прекратено и сега е класифицирано като остаряло, което означава, че Intel вече не произвежда или поддържа в активно производство.

Заключение

EPM7256AETC144-10N е мощен и гъвкав CPLD, който се използва в AI, 5G, облачни изчисления, индустриални машини, IoT и медицински изделия.Той обработва данните бързо, използва малко мощност и позволява лесно препрограмиране, без да ги отстранява от веригата.Той все още е полезен за по -стари дизайни, които се нуждаят от програмируема логика със стабилна производителност.Независимо дали работите с този CPLD или търсите подобни алтернативи, разбирането на неговия дизайн, програмиране и предимства може да ви помогне да го използвате най-добре при високоскоростни цифрови приложения.

DataSheet PDF

EPM7256AETC144-10N таблици с данни:

За нас

ALLELCO LIMITED

Прочетете още

Бързо запитване

Моля, изпратете запитване, ние ще отговорим незабавно.

често задавани въпроси [FAQ]

1. Колко логически елемента или порти могат да се справят EPM7256AETC144-10N?

EPM7256AETC144-10N осигурява 256 макроклета и приблизително 5000 използваеми порти, което позволява умерено сложни логически реализации.

2. Как да програмирам EPM7256AETC144-10N и какви инструменти имам нужда?

EPM7256AETC144-10N поддържа програмируемост в системата (ISP) чрез JTAG (IEEE 1149.1) интерфейс.Ще ви е необходим Altera USB-Blaster или Intel Quartus Prime Software, за да напишете конфигурационни данни в чипа.

3. Какви са разликите между EPM7256AETC144-10N и EPM7256AETC144-7?

Основната разлика е скоростта.EPM7256AETC144-10N има максимално забавяне на разпространението от 10 ns, докато EPM7256AETC144-7 има по-бързо 7 ns закъснение за приложения с по-висока скорост.И двете устройства споделят един и същ пакет, броя на I/O и структура на макроклета.

4. Изисква ли EPM7256AETC144-10N външен осцилатор?

Не, самият CPLD не изисква външен осцилатор, но поддържа външни входове на часовника.Ако вашият дизайн се нуждае от прецизно време, може да се използва външен часовник сигнал за задвижване на неговите логически операции.

5. Какво прави EPM7256AETC144-10N различен от другите CPLD в серията Max 7000a?

Този CPLD се откроява поради високоскоростните си показатели (10 NS закъснение на разпространение), 256 макроклета и 5000 използваеми порти, което го прави идеален за сложни логически дизайни.Той също така поддържа програмността на системата (ISP) чрез JTAG, за разлика от някои по-стари модели.

MPC8245LZU300D Процесор: Данте, функции, приложения и спецификации

на 2025/03/13

Просто ръководство за батерии L1154 за ежедневна употреба

на 2025/03/13

Популярни публикации

-

Компютри на сложни инструкции: Как промениха изчисленията?

на 8000/04/18 147767

-

USB-C Pinout и функции

на 2000/04/18 111994

-

Използване на Xilinx Unified Simulation Primitives: Изчерпателно ръководство за FPGA дизайн и симулация

на 1600/04/18 111351

-

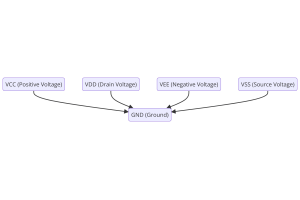

Захранващи напрежения в електрониката: Значение на VCC, VDD, VEE, VSS и GND

на 0400/04/18 83758

-

Ръководство за конектор RJ45: Pinout, окабеляване, видове кабели и употреби

на 1970/01/1 79555

-

Крайното ръководство за цветни кодове в съвременните електрически системи

Начинът, по който нашите електрически системи използват цветове, не е само за външен вид.Всеки цвят на проводника сега показва специфична функция, което улеснява идентифицирането и обработката на е...на 1970/01/1 66952

-

Ръководство за клапа на чист: функция, симптоми, тестване и подмяна на оптимална работа на двигателя

Клапанът на чистката е ключова част от системата на автомобила, която помага да се поддържа чистият въздух, като управлява изпаренията на горивото, преди да могат да избягат в атмосферата.Това не с...на 1970/01/1 63098

-

Качество (Q) Фактор: Уравнения и приложения

Коефициентът на качество, или „Q“, е важен при проверка на това колко добре работят индуктори и резонатори в електронни системи, които използват радиочестоти (RF).'Q' измерва колко добре веригата с...на 1970/01/1 63028

-

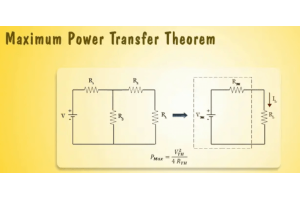

Постигане на пикова ефективност с теоремата за максимален трансфер на мощност

Теоремата за максимален пренос на мощност обяснява как енергия от източник, като батерия или генератор, преминава към свързан товар.Той показва точното състояние, при което товарът получава най -мн...на 1970/01/1 54094

-

Спецификации и съвместимост на батерията A23

Батерията A23 е малка батерия с форма на цилиндър с високо напрежение.Нарича се още 23A, 23AE или MN21, той работи на 12 волта и много по -високо от батериите на AA или AAA.Специалният му ...на 1970/01/1 52176