XCV200-6FG456C FPGA: функции, спецификации, програмиране и приложения

XCV200-6FG456C е мощен FPGA (полеви масив за програмиране на портата) от серията AMD Xilinx Virtex®.Това ръководство обяснява неговите характеристики, оформление на ПИН, стъпки за програмиране и употреби.С висока мощност на обработка, гъвкави опции за дизайн и силни възможности за вход/изход (I/O), тази FPGA помага за изграждането на бързи и надеждни цифрови системи.Независимо дали работите върху мрежови системи за управление или персонализирана електроника, това ръководство ще ви помогне да разберете как XCV200-6FG456C може да се използва във вашите проекти.Каталог

XCV200-6FG456C Преглед

The XCV200-6FG456C е забележителен модел в семейството на AMD Xilinx Virtex® FPGA, предназначен да предостави стабилни програмируеми логически решения за сложни цифрови системи.Този специфичен чип обхваща приблизително 236 666 системни порти и разполага с 1,176 конфигурируеми логически блока (CLBS) и 5 292 логически клетки.Той също така включва 57 344 общи бита на RAM и поддържа 284 I/O пина, разположени в пакет с масив с фина стъпка с 456 топка (FBGA), с размери 23 мм х 23 мм.Този модел работи на 2.5V номинална напрежение, с диапазон от 2.375V до 2,625V и може да функционира в температурен диапазон от 0 ° C до 85 ° C.По -широката серия Virtex® се грижи за редица приложения с плътност от 50 000 до над 1 милион системни порти и скорости на системния часовник до 200 MHz.Той поддържа многобройни I/O стандарти, включително LVTTL, LVCMOS и PCI, наред с други.Функции като закъснели бримки (DLLS), конфигурируеми логически блокове с вградена памет и специална логика за носене за аритметични операции подобряват неговата функционалност.Произведен с помощта на 5,22 µm 5-сложен метален процес, семейството на Virtex® гарантира производителност и надеждност.

Ако търсите да интегрирате FPGA технологията от най-високо ниво във вашите продукти или системи, закупуването на XCV200-6FG456C в насипно състояние с нас е интелигентен ход.Той отговаря на индустриалните стандарти и ви държи пред бъдещите технологични нужди.

XCV200-6FG456C функции

• Системни порти: XCV200-6FG456C предлага приблизително 236 666 системни порти.Този голям брой на портата позволява внедряването на сложни интегрирани цифрови логически схеми на един чип, подобрявайки както производителността, така и гъвкавостта в редица приложения.

• Логически ресурси: Тя включва 1,176 конфигурируеми логически блокове (CLBs) и 5 292 логически клетки.Тези ресурси са добри за проектиране на гъвкави и мащабируеми цифрови схеми.CLBS може да бъде програмиран за изпълнение на голямо разнообразие от логически функции, докато големият брой логически клетки позволява обработка на обширни логически операции и процеси.

• Памет: Устройството осигурява 57 344 бита RAM, разпределени между неговите логически блокове.Тази вградена RAM се използва за приложения, които изискват бързо и ефективно съхранение и извличане на данни, като поддържат високоскоростни операции с данни, неразделни за съвременните цифрови системи.

• Възможности за I/O.: С 284 входни/изходни пина, XCV200-6FG456C улеснява обширните възможности за взаимодействие.Тези I/O пинове поддържат различни стандарти за сигнала и позволяват на FPGA да комуникира ефективно с други компоненти в система, като устройства за памет, процесори и периферни устройства.

• Напрежение и температурен диапазон: Работейки при номинална напрежение от 2.5V, с приемлив диапазон от 2.375V до 2.625V, този FPGA е проектиран за консумация на ниска мощност, като същевременно поддържа стабилна работа.Той може да работи в рамките на температурата на съединението от 0 ° C до 85 ° C, като гарантира надеждността при различни условия на околната среда.

XCV200-6FG456C ПИН Функция диаграма

The XCV200-6FG456C ПИН Функция диаграма е структурирано представяне на задачите за ПИН на FPGA, категоризирани в различни банки (Банка 0 до банка 7).Всяка банкова групира пинове въз основа на тяхната функция и физическо разположение на пакета FPGA.Системата за номериране и етикетиране следва модел на мрежата, където редовете се обозначават с букви (A, B, C и т.н.) и колони по числа (1, 2, 3 и т.н.), което улеснява бързото идентифициране на специфични щифтове.Тези банки съответстват на различни функции на вход/изход, мощност, наземно и специализирано маршрутизиране на сигнала.На щифтовете се назначават различни функционални групировки, включително обща граница I/O (GPIO), често обозначени като "G" (общ вход/изход), "V" (захранване на напрежението) и "O" (изход).Мощността и наземните щифтове се маркират ясно, като гарантират стабилна работа на FPGA.Специално предназначени щифтове като входове на часовника, нулиране и контролни сигнали се идентифицират със символи като "R" или "T."Някои щифтове също обслужват специализирани комуникационни роли, включително JTAG конфигурация и високоскоростен часовник, за програмиране и отстраняване на грешки.

XCV200-6FG456C Блок-диаграма

Вход/изходен блок

Диаграмата представлява Вход/изходен блок (IOB) Структура на XCV200-6FG456C FPGA, която е член на семейството на Xilinx Virtex.Диаграмата показва ключови елементи, участващи във входните и изходните операции, като подчертава механизмите за поток и контрол на данните.В основата на диаграмата три джапанки се използват за регистриране на сигнали за вход, изход и Tri-State Control.Изходният регистър се контролира от сигнала на OCE (изходния часовник), който определя кога изходните данни са затворени.По същия начин, Tri-State Register се контролира от TCE (Tri-State Clock Anable), като се активира или деактивира изходния буфер.Входният регистър улавя входящите данни и прилага програмируемо забавяне, преди да го предаде на вътрешната FPGA логика чрез IBUF (входен буфер).Obuft (Tri-State изходен буфер) гарантира, че FPGA може да задвижва сигнал върху подложката (I/O щифт) или да го постави в състояние с висок импеданс, в зависимост от логиката на управление.В подложката е включена слаба верига на вратаря, за да се поддържа последното известно логическо състояние, когато няма активен драйвер, предотвратявайки непредвидени плаващи условия.Референтното напрежение (VREF) се използва за определени стандарти за вход, като SSTL или HSTL, които изискват точни нива на напрежение за правилна работа.Като цяло тази IOB структура позволява на FPGA да управлява високоскоростно предаване на данни, да поддържа различни входно/изходно стандарти и да осигури гъвкав контрол върху времето и целостта на сигнала.

Сериен режим на главен/подчинен

The Сериен режим на главен/подчинен Блок-диаграмата илюстрира процеса на конфигурация на Virtex FPGA, по-специално XCV200-6FG456C, когато се програмира в конфигурация на веригата за маргаритка, използвайки сериен EEPROM (XC1701L).В тази настройка едно Virtex устройство работи като главен, контролирайки конфигурационния часовник (CCLK) и серийно предаване на данни за конфигурация на допълнителни подчинени FPGA във веригата.Master FPGA инициира процеса на конфигуриране, като отстоява програмния сигнал, като нулира всички устройства във веригата.След като инициализацията приключи, сигналът на init показва готовност, а данните за конфигурацията се прелива от серийния EEPROM (XC1701L) към пина DIN (данни в) на главния FPGA.Главният FPGA чете данни от EEPROM и ги препраща през DOUT (DATA OUT) към следващите подчинени FPGAs, синхронизирайки трансфера на данни, използвайки сигнала CCLK.Полученият сигнал се използва за обозначаване на успешна конфигурация, като незадължителен резистор за изтегляне гарантира стабилно високо състояние, когато конфигурацията е завършена.XC1701L EEPROM се контролира от главния FPGA, използвайки CLK, данни, CE (Anable CHIP) и нулиране/OE (изходни активира) сигнали, като се гарантира, че съхраняваните данни за конфигурация са правилно извлечени.Този метод на конфигуриране е ефективен за програмиране на множество FPGAs с помощта на един EEPROM, намаляване на сложността на външната окабеляване и гарантиране на всички устройства да получават синхронизирани данни за конфигурация.

XCV200-6FG456C Спецификации

|

Тип |

Параметър |

|

Производител |

AMD Xilinx

|

|

Серия |

Virtex® |

|

Опаковане |

Табла |

|

Статус на част |

Остарял |

|

Брой лаборатории/CLB |

1176 |

|

Брой логически елементи/клетки |

5292 |

|

Общи битове на RAM |

57344 |

|

Брой на I/O. |

284 |

|

Брой порти |

236666 |

|

Напрежение - Захранване |

2.375V ~ 2.625V |

|

Тип монтаж |

Повърхностно монтиране |

|

Работна температура |

0 ° C ~ 85 ° C (TJ) |

|

Пакет / случай |

456-BBGA |

|

Пакет устройства за доставчици |

456-FBGA (23x23) |

|

Основен номер на продукта |

Xcv200 |

Приложения XCV200-6FG456C

Телекомуникации и работа в мрежа

XCV200-6FG456C превъзхожда телекомуникационните и мрежовите приложения поради способността си да обработва високоскоростни предавания на данни и сложни задачи за обработка на сигнали.Неговият голям брой на портата и стабилни възможности за входна/изходна помощ позволяват да поддържа функции като обработка на пакети, модулация/демодулация на сигнала и протоколи за корекция на грешки.

Обработка на цифрови сигнали (DSP)

Идеален за DSP приложения, тази FPGA може да извършва бързи и сложни математически изчисления, необходими в технологиите за аудио и видео обработка.Независимо дали става въпрос за мултимедийни системи, разпознаване на глас или стрийминг услуги, мощните възможности за обработка на XCV200-6FG456C и вградената памет поддържа ефективна и висококачествена обработка на сигнала.

Системи за индустриален контрол

В индустриалната автоматизация XCV200-6FG456C осигурява необходимата производителност за управление на системи за управление и мрежи за автоматизация.Способността му да изпълнява множество задачи за управление едновременно, като същевременно гарантира, че времето за реакция го прави подходящ за приложения в контрола на процесите, роботиката и машинното зрение.

Медицински инструменти

Прецизността и скоростта на FPGA са чудесни при медицинско изображения и диагностично оборудване, където подпомага обработката на сложни алгоритми за приложения за изображения като ЯМР, ултразвук и КТ сканиране.Възможностите на XCV200-6FG456C гарантират, че той може да се справи с висока пропускателна способност и сложна обработка, необходима в съвременната медицинска технология.

XCV200-6FG456C Подобни части

XCV200-6FG456C стъпки за програмиране

Стъпки за програмиране за XCV200-6FG456C:

1. Запис на дизайн

Първоначалната фаза на програмирането на FPGA включва дефиниране на цифровата логика и функционалността на вашата система.Това може да се направи с помощта на езици за описание на хардуер (HDL) като VHDL или Verilog, където пишете код, който уточнява как FPGA обработва данни и взаимодейства с друг хардуер.Схематичните инструменти за влизане, налични в FPGA дизайнерски софтуер като Xilinx ISE или Vivado, могат да бъдат използвани.Този метод включва създаване на визуално представяне на логиката чрез плъзгане и пускане на компоненти, които някои намират за по -интуитивно от писането на код.

2. Синтез

След като дизайнът приключи, следващата стъпка е синтез, при който инструмент като XST на Xilinx (Xilinx Synthesis Technology) трансформира вашия HDL код или схематичен дизайн в NetList.Този NetList описва схемата по отношение на общи цифрови компоненти, като логически порти и регистри.Процесът на синтез също включва оптимизиране на дизайна, за да отговаря на изискванията за производителност и да се сведе до минимум използването на ресурси за ефективна работа на FPGA.

3. Изпълнение

Процесът на внедряване започва с превод, комбинирайки вашия дизайн с ограничителни файлове, които определят параметри като честоти на часовника и задачи на ПИН.След превод, етапът на картографиране присвоява елементите на вашия NetList на специфични физически ресурси на FPGA, като таблици за търсене (LUTS) и джапанки.След това фазата на разположение и маршрутизиране определя физическите места на всеки компонент в архитектурата на FPGA и установява връзките между тях чрез програмируеми ресурси за взаимосвързаност.Този етап е чудесен за постигане на желаните показатели за производителност, включително честоти на часовника.

4. Поколение на битстрийм

След успешното поставяне и маршрутизиране инструментът генерира битстрийм, двоичен конфигурационен файл, който съдържа цялата информация за програмиране за FPGA.Често се препоръчва да се симулират окончателното дизайнерско след поставяне, за да се гарантира, че битстъм ще се държи според очакванията при условия.Тази стъпка на проверка помага да се избегнат потенциални проблеми по време на действителната работа.

5. Конфигурация

Последната стъпка включва зареждане на битстрийма в FPGA с помощта на различни методи за конфигурация.Режимът на подчинените серии, проста и рентабилна опция, конфигурира FPGA чрез външно главно устройство, което изпраща данни серийно.В главно-сериен режим FPGA автономно чете битстрийма от прикачен сериен бал.За високоскоростни конфигурации режимът SelectMap позволява на външен микропроцесор бързо да зарежда данни във FPGA.Освен това, JTAG режимът се използва не само за програмиране, но и за тестване и отстраняване на грешки, използвайки стандартен интерфейс за програмиране в системата и тестване на гранично-сканиране.

XCV200-6FG456C Предимства

Изпълнение

Серията Xilinx Virtex, към която принадлежи XCV200-6FG456C, е оптимизирана за високоскоростна производителност, предлагайки скорости на системен часовник до 200 MHz.Това го прави подходящ за приложения, които изискват бърза обработка на данни, като се гарантира ефективно обработка на сложни алгоритми и високоскоростни операции като телекомуникации, обработка и мултимедия.

Поддръжка на стандарти за I/O

Тази FPGA поддържа широк спектър от стандарти за вход/изход, включително LVTTL, LVCMOS, PCI, GTL, HSTL, SSTL, CTT и AGP.Такава обширна поддръжка на стандарти за входно/изходно ниво позволява на XCV200-6FG456C да се интегрира безпроблемно с различни системни компоненти, подобрявайки неговата полезност в различни цифрови екосистеми.Тази гъвкавост позволява да се адаптира FPGA към различни условия на взаимодействие без модификации на системата.

Управление на часовника

XCV200-6FG456C включва множество заключени закъснения бримки (DLLS) за разпределение и управление на часовника в системата.Тези DLLs помагат за подобряване на времето и надеждността на системата чрез предоставяне на прецизни сигнали на часовника, необходими за синхронни операции.Тази функция е важна за намаляване на системните грешки и повишаване на общата производителност, особено в сложни дизайни, изискващи точни времена и синхронизация.

Дизайн гъвкавост

С 1,176 конфигурируеми логически блокове и 5 292 логически клетки, XCV200-6FG456C предлага значителни логически ресурси с възможност за прилагане на разнообразен набор от функционалности.От проста логика на лепилото до сложните цифрови системи, тази FPGA поддържа сложни дизайнерски изисквания, което го прави идеален за приложения в персонализирани изчисления, обработка на цифрови сигнали и прототипиране.

Бързо прототипиране

FPGA като XCV200-6FG456C са известни с способността си да поддържат бързо прототипиране.Това устройство позволява бързо проектиране на дизайна и може да бъде преконфигурирано в полето, което е предимство за цикли на развитие, тъй като намалява времето до пазара.Той също така се адаптира ефективно към променящите се изисквания или актуализации в спецификациите на проекта, като гарантира, че крайните продукти са актуални с най-новите технологични стандарти.

Възможност за интеграция

Възможностите за интеграция на XCV200-6FG456C улесняват консолидирането на множество дискретни компоненти в един чип.Тази интеграция може да доведе до намалена сложност на системата, по -ниска консумация на енергия и икономия на разходи.Чрез минимизиране на броя на необходимите отделни компоненти, това FPGA опростява дизайнерските процеси и подобрява надеждността и компактността на цялостната система.

XCV200-6FG456C Размери на опаковките

XCV200-6FG456C е полеви програмируем масив на портата (FPGA) от серията Virtex® на AMD, разположен в пакет с фина стъпка с фина стъпка с 456-топка (FBGA).

• Тип пакет: 456-FBGA

• Размер на пакета: 23 mm x 23 mm

• Топка стъпка: 1.0 mm

Производител на XCV200-6FG456C

XCV200-6FG456C е полеви програмируем масив на портата (FPGA), първоначално разработен от Xilinx, компания, известна със своите високоефективни програмируеми логически устройства.След придобиването на Xilinx от AMD, XCV200-6FG456C вече е свързан с AMD като настоящ производител.Този модел на FPGA обаче е остарял и вече не е в производство.AMD продължава да поддържа по -новите FPGA архитектури с повишена производителност, ефективност на мощността и продължително дълголетие, което прави съвременните алтернативи за за предпочитане за новите дизайни.

Заключение

XCV200-6FG456C е универсален и високоскоростен FPGA, полезен за много технологични приложения.Въпреки че вече не се прави, той все още е добър избор за по -стари системи, които се нуждаят от надеждна производителност.Това ръководство обхвана своите дизайнерски стъпки, програмиране и практически приложения, което улеснява разбирането на това как работи и как може да се използва.Тъй като по -новите FPGA стават достъпни, можете да използвате тези знания, за да изберете правилния FPGA за вашите нужди и да подобрите цифровите дизайни.

DataSheet PDF

XCV200-6FG456C Данни таблици:

За нас

ALLELCO LIMITED

Прочетете още

Бързо запитване

Моля, изпратете запитване, ние ще отговорим незабавно.

често задавани въпроси [FAQ]

1. Каква е консумацията на енергия на XCV200-6FG456C?

XCV200-6FG456C работи на 2.5V, с диапазон на напрежение от 2.375V до 2.625V.Консумацията на енергия зависи от използването на логиката и честотата на часовника, но като по-стара FPGA може да е по-малко ефективна от по-новите устройства Xilinx.Трябва да се вземат предвид правилното управление на мощността и разсейването на топлината.

2. Как XCV200-6FG456C се сравнява с XCV200-6FG256C?

XCV200-6FG456C има по-голям пакет (456-топка FBGA) в сравнение с XCV200-6FG256C (256-топка FBGA), предлагайки повече I/O пинове (284 срещу 172) и потенциално по-добри резултати за приложения, изискващи обширни взаимодействия.Ако вашият дизайн разчита на повече възможности за I/O, XCV200-6FG456C е по-добрият избор.

3. Мога ли да препрограмирам XCV200-6FG456C многократно?

Да, XCV200-6FG456C е FPGA на базата на SRAM, което означава, че може да бъде препрограмиран с неограничен брой пъти, докато се доставя мощност.Въпреки това, ще се нуждаете от външна не-променлива памет (EEPROM или FLASH), за да запазите битстрийма след цикъл на захранване.

4. Поддържа ли XCV200-6FG456C високоскоростната серийна комуникация?

XCV200-6FG456C поддържа множество I/O стандарти като LVTTL, LVCMOS, PCI, GTL, HSTL и SSTL, но няма вградени високоскоростни SERDES (сериалайзер/deserializer) или трансцентри като съвременни FPGAs.За приложения, изискващи високоскоростни серийни връзки (например PCIE, Gigabit Ethernet или HDMI), помислете за по-нови FPGA модели.

5. Как XCV200-6FG456C се сравнява с по-новите FPGA модели?

XCV200-6FG456C принадлежи към по-старо поколение FPGA.В сравнение със съвременния Virtex FPGAS, той има по -нисък брой на портата, по -бавни тактови скорости и ограничена ефективност на мощността.По -новите модели предлагат по -висока логическа плътност, по -вградена памет, усъвършенствани DSP блокове и по -ниска консумация на енергия, което ги прави по -добри за съвременните приложения.

AD73322AR Pinout, функции и технически подробности обяснени

на 2025/03/21

EP20K100EFC324-1X FPGA: Функции, спецификации, приложения и ръководство за програмиране

на 2025/03/20

Популярни публикации

-

Компютри на сложни инструкции: Как промениха изчисленията?

на 8000/04/18 147765

-

USB-C Pinout и функции

на 2000/04/18 111989

-

Използване на Xilinx Unified Simulation Primitives: Изчерпателно ръководство за FPGA дизайн и симулация

на 1600/04/18 111351

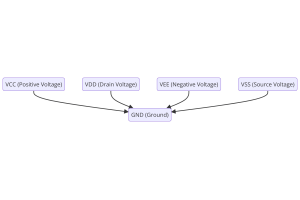

-

Захранващи напрежения в електрониката: Значение на VCC, VDD, VEE, VSS и GND

на 0400/04/18 83751

-

Ръководство за конектор RJ45: Pinout, окабеляване, видове кабели и употреби

на 1970/01/1 79546

-

Крайното ръководство за цветни кодове в съвременните електрически системи

Начинът, по който нашите електрически системи използват цветове, не е само за външен вид.Всеки цвят на проводника сега показва специфична функция, което улеснява идентифицирането и обработката на е...на 1970/01/1 66949

-

Ръководство за клапа на чист: функция, симптоми, тестване и подмяна на оптимална работа на двигателя

Клапанът на чистката е ключова част от системата на автомобила, която помага да се поддържа чистият въздух, като управлява изпаренията на горивото, преди да могат да избягат в атмосферата.Това не с...на 1970/01/1 63094

-

Качество (Q) Фактор: Уравнения и приложения

Коефициентът на качество, или „Q“, е важен при проверка на това колко добре работят индуктори и резонатори в електронни системи, които използват радиочестоти (RF).'Q' измерва колко добре веригата с...на 1970/01/1 63028

-

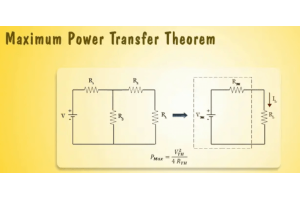

Постигане на пикова ефективност с теоремата за максимален трансфер на мощност

Теоремата за максимален пренос на мощност обяснява как енергия от източник, като батерия или генератор, преминава към свързан товар.Той показва точното състояние, при което товарът получава най -мн...на 1970/01/1 54092

-

Спецификации и съвместимост на батерията A23

Батерията A23 е малка батерия с форма на цилиндър с високо напрежение.Нарича се още 23A, 23AE или MN21, той работи на 12 волта и много по -високо от батериите на AA или AAA.Специалният му ...на 1970/01/1 52174